首款嵌入式FPGA誕生 AI將迎來最好時代?

eFPGA如何做到帶寬增加10倍延遲減小至1/10

本文引用地址:http://www.j9360.com/article/201610/311373.htmRobert Blake為包括電子發燒友在內的媒體解密了Speedcore eFPGA為何能在互聯帶寬增加10倍、互聯延遲減小至1/10的提升下還能將功耗降低50%,成本降低90%。

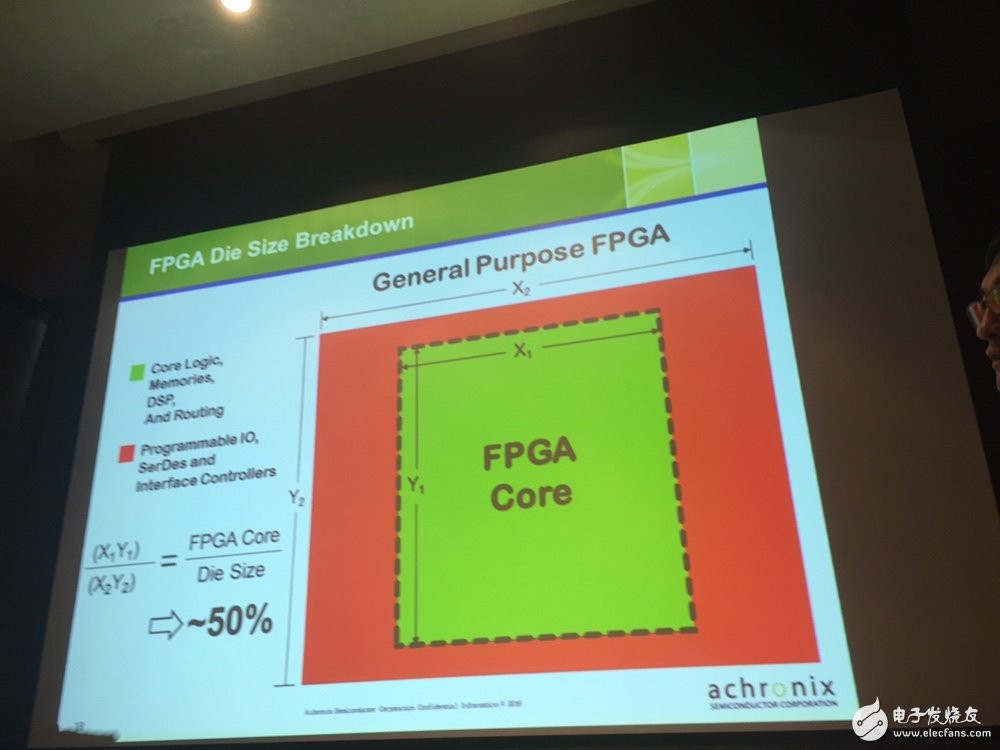

要嵌入到SoC中首先需要解決FPGA芯片的面積問題,標準的FPGA內核與可編程IO、控制器等面積比接近1:1。Achronix 的Speedcore eFPGA直接連接至SoC,不僅能夠將FPGA芯片面積減少一半,使FPGA能夠嵌入到SoC中,還能夠減小CB的尺寸、減少PCB的層數以及提高信號完整性。

圖:eFPGA面積減小一半

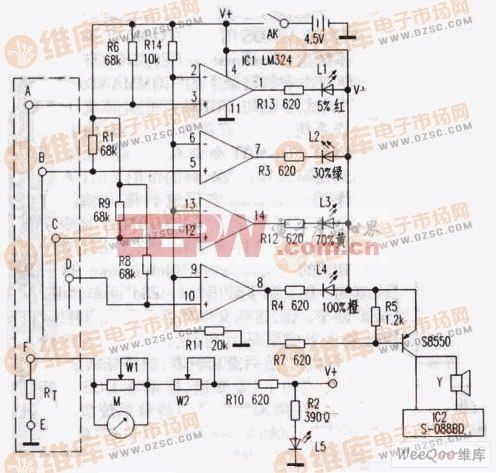

Speedcore以內部連線方式直接連接至SoC,省去了在外置獨立FPGA中可見的大型可編程輸入輸出緩沖(IO buffer),能耗得到了降低。另外,Speedcore省去了對獨立FPGA周邊所有支持性元器件的需求,這些元器件包括電源調節器、時鐘發生器、電平位移器、無源元件和FPGA冷卻器件,成本也就相應的降低。

圖:Speedcore eFPGA功耗及成本的降低

圖:Speedcore與標準FPGA的帶寬及延遲時間對比

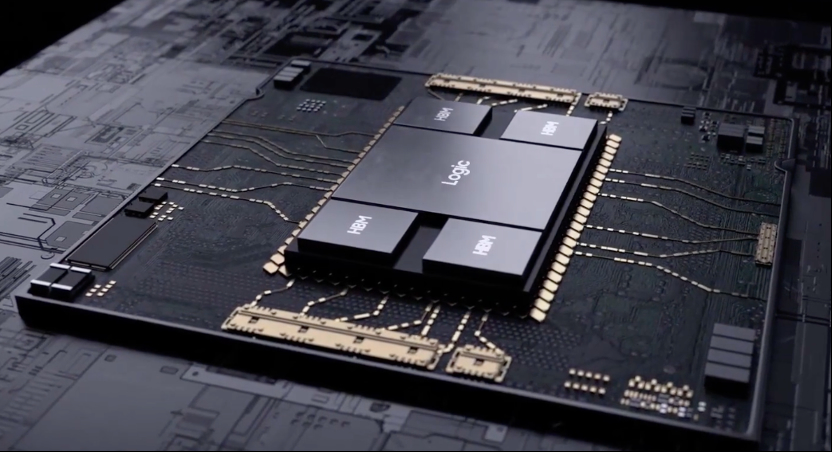

至此,對于eFPGA能比標準FPGA增加10倍帶寬以及延遲減小至1/10也就容易理解了。由于減小了FPGA芯片面積,大大節省了信號的傳輸時間,信號可以直接進入,可以將延遲時間降低到2ns,甚至0ns。而由于嵌入到SoC當中,帶寬也能夠增加十倍之多。

eFPGA工藝技術及工具

Achronix 的eFPGA目前主要瞄準計算中心、網絡以及5G應用,而Speedcore以模塊化方式構建,不僅可以在定義資源時提供靈活的支持,也能針對需求快速配置Speedcore IP 產品以實現交付。此外,模塊化架構也支持Achronix方便地將這項技術移植到不同的工藝技術和金屬疊層上。

圖:Speedcore模塊化架構

Robert Blake表示:“我們現在已經可以提供基于臺積電(TSMC)的16納米FinFET Plus(16FF+)工藝的Speedcore IP產品,并且正在開發基于臺積電的7納米工藝的IP。根據客戶的需求,如果需要轉換到新的工藝需要4到6個月的時間,之后針對不同核的支持則僅需要幾周的時間。”

隨著集成度的提升,對于FPGA而言軟件工具也十分重要。Achronix提供的ACE設計工具可以在性能、資源使用和編譯時間等方面評估Speedcore IP。此外,Achronix擁有關于Speedcore功能和ASIC集成流程方面的完整文檔。

圖:Achronix商業模式

除了開頭提到的英特爾,谷歌也推出了TPU(Tensor Processing Unit)芯片用于機器學習,因此我們相信未來FPGA將迎來應用于人工智能(AI)的好時機,而eFPGA未來也將會在不斷增長的高性能計算應用市場得到廣泛應用。

圖:Achronix Speedcore 嵌入式FPGA出貨

評論