讓電子系統的心跳更加強勁

2005年,IDT收購集成電路系統(ICS)業務后成為業界領先的時鐘時序集成電路解決方案供應商。而在今年3月正式完成對IDT的收購之后,其豐富的時鐘分發和時鐘合成器產品、以及尖端系統時序解決方案均納入瑞薩電子旗下,從而使瑞薩具備了業界最低相位噪聲和最高性能,最豐富最全面的時鐘產品組合,能滿足幾乎任何應用的任何嚴苛的系統需求。

本文引用地址:http://www.j9360.com/article/201911/406932.htm“時鐘IC”是一個廣義上的術語,用于描述可在電子系統中生成、調制、操縱、分發或控制計時信號的集成電路。在電平高和低狀態之間振蕩,并被用作節拍器來協調電路,這是時鐘計時信號最基本的職責。然而,在目前最先進的系統中應用時,時鐘IC還必須能夠生成精確的時鐘脈沖,并持續可靠地分發該信號以供系統中的各種計時設備使用。當以如此之高的速度運行時,系統設計和環境因素使保持信號質量變得極富挑戰性,通常會導致較高的位錯誤率(BER)和系統性能降級。

晶體振蕩器(Oscillator)

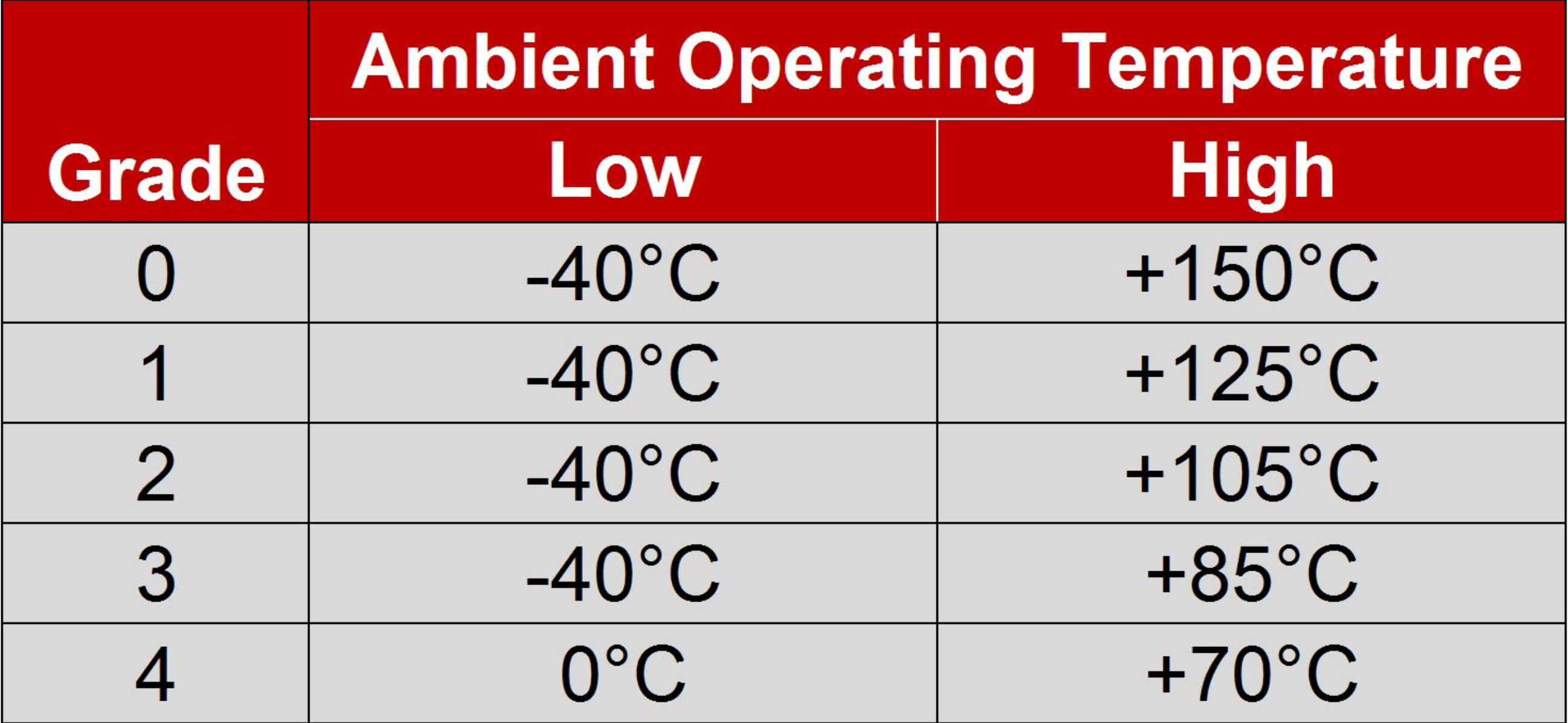

瑞薩提供晶體振蕩器(XO)。其中XL、XA(滿足AEC-Q200標準)和XU屬于高性能晶體振蕩器系列,采用行業標準封裝(3.2 x 2.5mm、5 x 3.2mm、7 x 5mm)和引腳,可提供HCMOS、LVPECL、LVDS 和HCSL輸出。XU和XL/XA系列分別擁有300fs和750fs RMS相位抖動(12kHz-20MHz),同時提供±20ppm/±25ppm/±50ppm/±100ppm的精度選項、以及16kHz至1.5GHz的自定義頻率,適用于網絡、可視系統、信息娛樂、通信、數據 I/O、存儲和服務器等相關應用。

今年5月推出的新型ProXO系列可編程、超低噪聲時鐘振蕩器,則具有加速器卡、100G和400G交換機以及數據中心、通信基礎設施和工業應用中使用的光學收發器所需的關鍵低相位噪聲時鐘功能,ProXO支持多種封裝、具有低于120fs相位抖動性能、允許1.8V-3.3V輸入電壓、內置獨立諧振器、可在線配置五種可選輸出類型(LVDS、CML、LVPECL、LVCMOS和HSCL)、輸出頻率亦可在線設置等特點,最大可能的滿足客戶的高性能、靈活可變和可靠性方面的要求。

時鐘產生(Clock Generator)

l 可編程時鐘發生器

可編程時鐘發生器(也被稱為可編程計時裝置)可幫助設計人員通過取代晶體、振蕩器、和含有單一計時裝置的緩沖器的方式節省電路板空間和成本,這使得它們極其適合于消費品、數據通信、電信和計算等應用。瑞薩的可編程時鐘發生器系列包括通用頻率轉換器(UFT)、FemtoClock NG、MicroClock以及VersaClock等系列,每種產品均提供不同級別的抖動性能、能耗、靈活性以及成本,最大可能滿足不同應用需求的客戶。

——MicroClock時鐘發生器

微型可編程時鐘發生器(MicroClock)最新產品5X1503和5L1503非常適合用于需要小尺寸和超低功耗的緊湊型便攜式產品應用。5X1503/5L1503器件的尺寸僅為2.0 x 2.0mm,可顯著縮減80%以上的電路板面積,具有3路獨立可編程LVCMOS輸出,輸出頻率高達100MHz且部分產品支持展頻(Spread spectrum)功能。另外,該時鐘發生器的三路輸出均支持32.768kHz實時參考時鐘(RTC),并且在省電模式下僅需消耗1μA電流,可讓裝置單靠一顆220mAh鈕扣電池就能運行12年以上。

——VersaClock 3S

VersaClock 3S系列可編程時鐘發生器集低功耗、高靈活性和高性能于一身,可通過替代多個分立式時鐘組件簡化設計,也可以通過降低BOM和縮小電路板空間來降低成本,從而為消費類電子產品、數據通信、電信以及網絡應用提供了前所未有的多樣性。

該產品系列可支持從1.8到3.3V的工作電壓、差分(LVPECL/HCSL/LVDS/LP-HCSL)和 LVCMOS輸出類型、支持高達3個PLL和多個分數分頻器,以便能夠準確生成幾乎任何頻率。產品可滿足各種系統要求,如取代振蕩器、支持PCIe Gen 1/2/3,同時具有極低的功耗。

——VersaClock 6系列

該系列為VersaClock 3S的升級產品,除了具備VersaClock 3S的特點外,其具備更好的RMS相位抖動(低于500fs)和更寬的輸出時鐘頻率范圍(

1kHz to 350MHz)。其浮點型分頻器支持更精細的輸出頻率要求,內置OTP可提供4種預配置和支持通過I2C總線進行在線配置,同時符合PCIe Gen 1/2/3/4標準。

l PCIe 時鐘發生器

PCIe作為高速串行通信接口,其 PCIe Gen4 協議最高速度可達16Gb/s。與任何串行通信接口一樣,相位抖動是最關鍵的時鐘參數,這使得PCIe時鐘發生器成為PCIe設計的關鍵器件之一,是系統性能和可靠性的決定因素。PCIe系統如果使用低性能時鐘鏈接可能趨向于低于標榜的吞吐量,或發生大量鏈接錯誤,從而必須重新發送數據,甚至會無法正常工作。

瑞薩PCIe時鐘發生器提供1 到8個輸出端,完全滿足PCIe 1/2/3/4 規格要求 。集成式終端可將輸出直接連接至傳輸線路,從而節省大量電路板空間。此外,瑞薩還提供1.5V、1.8V 或3.3V版本的高性能時鐘發生器,使設計人員能夠從其芯片的FPGA或系統中的同一電源向PCIe時鐘發生器供電。

l EXCALIBUR系列

該系列屬于超低噪聲時鐘發生器,8V4xNS0x12 FemtoClock時鐘發生器系列在四組獨立的分頻器中設有12路輸出,具有三個整數輸出分頻器和一個小數輸出分頻器,支持頻率高達2500MHz的以太網、同步光纖網絡(SONET)以及通用公共無線電接口(CPRI),無需單獨的時鐘域和扇出緩沖器,因此降低了物料清單(BOM)成本并簡化了設計,適用于通信和數據通信市場的高性能時序,尤其適用于需要極低相位噪聲的應用。

時鐘分配(Clock Distribution)

時鐘分配產品用于在使用或不使用鎖相環路(PLL)的情況下,在系統中調節、扇出并分配時鐘信號。這些器件非常適合于大多數輸入信號質量良好的應用,其目標是緩沖、扇出、分配或多路復用輸入信號。單輸出時鐘緩沖器還用于將時鐘從一個信號標準轉化成另一個標準(例如將LVCMOS輸入轉化成LVPECL輸出)。

作為計時解決方案的行業領導者,瑞薩提供豐富的時鐘緩沖器、時鐘分配和多路復用器解決方案組合,這些器件支持的最常見的LVDS、LVPECL、HCSL、LVCMOS、CML、HSTL、SSTL等類型,可滿足幾乎任何應用的需求。

5PB11xx系列是低功耗LVCMOS扇出緩沖器的典型代表。新緩沖器可提供2、4、6、8和10路LVCMOS輸出,并可以支持1.8V、2.5V和3.3V的電源和輸出,其均方根附加相位抖動(12kHz至20MHz)不到50fs,并且只有14mA的內核電流消耗。與競爭產品相比,可為系統設計師提供更大的抖動容限,幫助他們滿足系統時鐘的要求。新緩沖器系列所有器件均采用2mm×2mm DFN 8引腳封裝,也均可在-40℃至105℃的擴展溫度下工作,適合于高端消費電子產品、工業、數據通信、電信和計算等時序應用。

而5P83904是一顆具備1-4路無源晶體輸入的高性能LVCMOS扇形輸出緩沖器,采用標準TSSOP或小型QFN封裝,可在1.8V到3.3V電源之間工作。該器件支持10MHz到40MHz的無源本振晶體輸入,并可輸出同類最佳相位噪聲性能的LVCMOS時鐘。此外,5P83904具有同步無故障輸出啟用功能,可在啟用或禁用輸出時消除任何中間錯誤輸出時鐘周期。

IDT PCIe分配器則擁有2到19路不等的輸出范圍,能夠滿足PCI Express Gen 1、Gen 2、Gen 3和Gen 4的要求。IDT提供內置PLL的PCIe分配器以滿足零時延要求或無內置PLL的PCIe分配器等多種選擇,同時其輸出端還內置不同阻值(33Ω/85Ω/100Ω)的端接電阻以降低客戶電路板設計難度、減小電路板尺寸和提高系統可靠性。以9DBL0941為例,這是瑞薩3.3V全功能PCIE時鐘系列的一個成員,支持PCIE Gen1-4共模時鐘(CC)和PCIE獨立展頻時鐘(SRIS)系統,其輸出端還提供了100Ω的端接電阻。

抖動衰減器(Jitter Attenuator)

抖動衰減器可從一個或多個輸入時鐘信號中消除不需要的噪聲,從而滿足嚴苛的時鐘抖動需求。該系列產品的不同型號使用 VCXO 或簡單晶體作為參考,支持使用固定頻率晶體。此外,抖動衰減器產品還包括頻率轉換部分,支持輸出頻率與輸入頻率完全不同。這種輸入-輸出頻率可根據所選器件采用整數分頻或浮點型分頻。該系列中的器件均支持靈活分頻,從而提供多種獨立頻率。

將抖動衰減器和頻率轉換器集成在一起的做法簡化了電路,同時也將物料清單(BOM)減至最少。 瑞薩豐富的抖動衰減器和頻率轉換器產品組合具有不同級別的性能、功耗和可編程性,支持各種單端和差分信號級,如 LVCMOS、LVPECL、LVDS、HCSL、HSTL 或 SSTL等,可以滿足幾乎任何應用的需求。

8T49N240 FemtoClock? NG通用頻率轉換器設有單通道浮點反饋PLL,可用作抖動衰減器或頻率合成器的頻率轉換器。8T49N240配有三個整數和一個浮點輸出分頻器,最多可產生四個不同的輸出頻率(8kHz至867MHz)。這些頻率完全獨立于輸入時鐘參考頻率和晶體參考頻率,輸出可以在LVPECL、LVDS、HCSL或LVCMOS輸出電平之間進行靈活選擇。

評論