2.5 Gbps收發器中相位鎖定檢測電路的設計與仿真

摘要:相位鎖定檢測電路是鎖相環 環路的關鍵電路,其性能的優劣直接影響了整個系統的工作。本文描述了相位鎖定檢測電路的工作原理,根據項目實際提出一種相位鎖定檢測方案,按照全定制設計流程采用SMIC0.18μm CMOS混合信號工藝完成了電路的設計、仿真。結果表明該電路在2.5Gbps收發器電路中可以穩定可靠地工作。

環路的關鍵電路,其性能的優劣直接影響了整個系統的工作。本文描述了相位鎖定檢測電路的工作原理,根據項目實際提出一種相位鎖定檢測方案,按照全定制設計流程采用SMIC0.18μm CMOS混合信號工藝完成了電路的設計、仿真。結果表明該電路在2.5Gbps收發器電路中可以穩定可靠地工作。

鎖相環 是高速多通道串行收發系統中的關鍵電路,相位是否準確對齊對于系統性能有著重要影響。電荷泵鎖相環

是高速多通道串行收發系統中的關鍵電路,相位是否準確對齊對于系統性能有著重要影響。電荷泵鎖相環 因其穩定性高,捕獲范圍大,便于集成等特點而別廣泛應用于無線通信、頻率綜合器和時鐘恢復電路中,為保證系統性能,鎖相環

因其穩定性高,捕獲范圍大,便于集成等特點而別廣泛應用于無線通信、頻率綜合器和時鐘恢復電路中,為保證系統性能,鎖相環 通常都集成了相位鎖定檢測電路。

通常都集成了相位鎖定檢測電路。

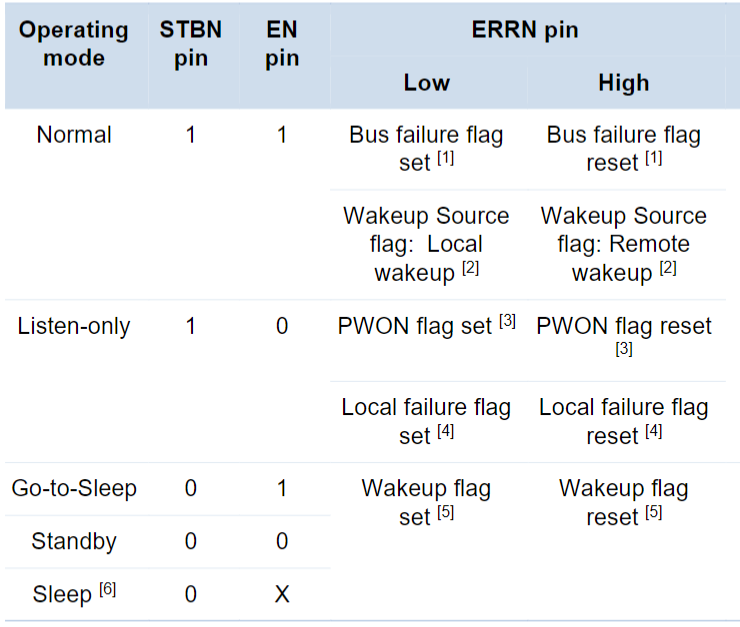

相位鎖定檢測電路通常包括模擬鎖定檢測和數字鎖定檢測兩種方法,模擬檢測方法采用經鑒頻鑒相器PFD輸出的相位誤差,產生脈沖信號對外部電容進行充電和放電,以指示當前相位是否鎖定,精度往往較低;數字鎖定檢測方法具有可編程性且設計易于實現等優點,但相位誤差參數受鎖相環工作環境的影響較大,可能導致相位誤差超出鎖相環的最大鎖定窗口。

本文根據2.5 Gbps高速串行收發器的工作實際,設計了雙環時鐘數據恢復電路中鎖相環路的相位檢測電路,該電路模擬和數字方法,采用全定制的數字設計,電路工作精度高,可以達到時鐘周期的1/218,能夠滿足G比特級數據收發的性能要求。電路采用SMIC 0.18μm CMOS工藝實現并基于spectre進行仿真,結果顯示電路可以正常工作,符合預期要求。

1 鎖定檢測電路的結構

電荷泵結構的鎖相環南鑒頻鑒相器(PFD)、電荷泵(CP)、低通濾波器(LPF)、壓控振蕩器(VCO)和分頻電路組成。鑒頻鑒相器比較輸入參考時鐘和反饋時鐘的頻率、相位誤差,當反饋時鐘落后于參考時鐘(即正相差)時,產生UP信號;當反饋時鐘超前于參考時鐘時(即負相差)產生DOWN信號。電荷泵連接PFD和濾波器LPF,它實際是一個電壓/電流轉換器,將PFD輸出的誤差電壓電壓轉換成電流對低通濾波器進行充電、放電,通過低通濾波器轉換為壓控振蕩器的控制電壓的升高或降低,從而調整壓控振蕩器輸出時鐘相位累積的快慢,分頻電路將VCO的輸出時鐘進行分頻后送給PFD,與外部參考時鐘進行比較,以輸出頻率、相位誤差脈沖,鎖定檢測電路用于時鐘的相位對齊檢測,保證輸入到時鐘數據恢復環路的時鐘的穩定。

在本文設計電路所應用的環境中,鎖相環輸入的外部參考時鐘頻率為125 MHz,而分頻器的分頻比為20,那么VCO的輸出時鐘頻率為2.5 GHz,但由PLL環路送給收發器中時鐘數據恢復電路的是1.25 GHz的時鐘,因此應將VCO的輸出信號經過一個二分頻及相位調整電路后才可以送給收發器供時鐘數據恢復電路使用。

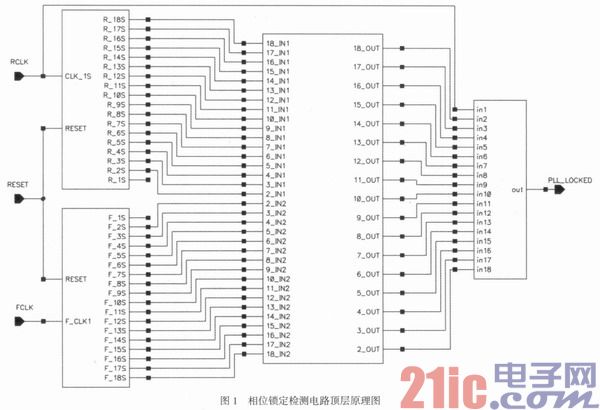

本文設計的相位鎖定檢測電路結構如圖1所示。該電路主要包括兩個可實現218分頻的分頻電路、18組兩輸入異或門構成的相位比較電路、一個18輸入或非門構成鎖定檢測電路。輸入參考時鐘和反饋時鐘分別進行18級分頻,各級分頻信號對應異或,其異或結果送給18輸入的或非門。當各級分頻時鐘對應相同時,則異或門輸出為0,此時經時序輸出PLL_LOCKED信號為低電平表示鎖定。

1)18級分頻電路

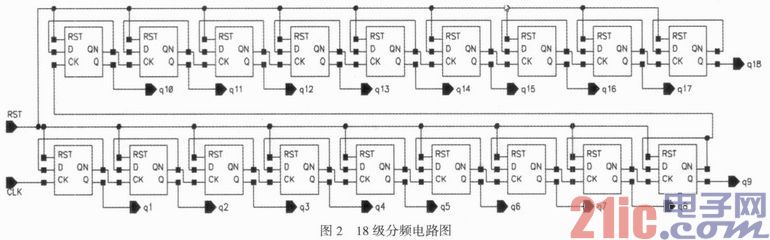

由于將D觸發器的輸出端取反后連接到輸入端,則輸出信號即為時鐘信號的2分頻。因此要對時鐘進行218分頻,則只需由將18個D觸發器依次級聯即可,電路如圖2所示。每個D觸發器采用主鎖存器為負鎖存器、從鎖存器為正鎖存器的主從結構,上升沿觸發,帶有異步復位,經過仔細地參數設計,觸發器工作頻率可以達到2.5 GHz以上,滿足電路的工作速度要求。

2)相位比較電路

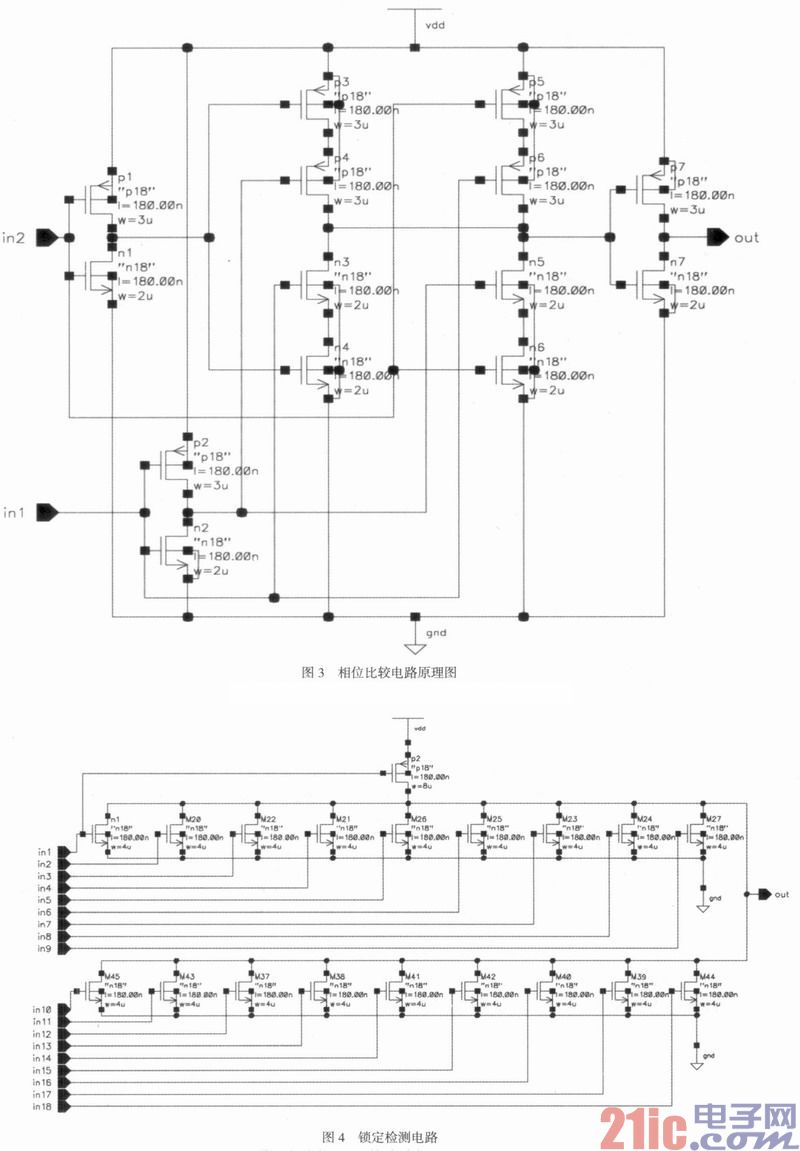

相位比較電路由18組獨立的兩輸入異或門構成,每個異或門用于比較鎖相環的參考時鐘的18個分頻輸出與由壓控振蕩器產生并經20分頻后得到的時鐘的18個分頻結果,達到在時鐘周期的1/18精度上的相位對齊。為了保證電路工作的時序要求,異或門的參數也經過仔細設計與調試,可以滿足性能要求。異或門電路如圖3所示。

3)鎖定檢測電路

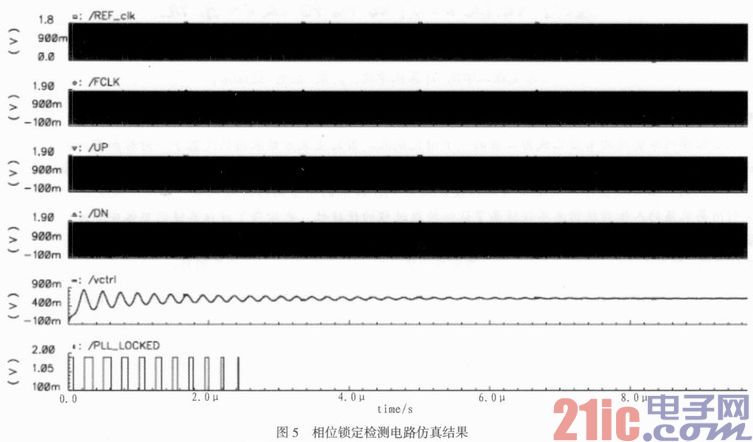

鎖定檢測電路由一個18輸入的準NMOS或非電路構成,在設計時可以增加一點考慮:這里的或非門是18輸入,而且若時鐘的第一級分頻結果就不相同,則之后各級均不相同。因此可將第一級分頻結果同時作為或非門的偏置信號,可以起到低功耗控制的作用。電路如圖4所示。

2 電路仿真

為驗證電路的功能性能是否符合要求,采用smic0.18μmCMOS工藝完成電路設計后,在cadence的spectre上進行仿真,仿真結果如圖5所示。從圖中可以看出當輸入時鐘和反饋時鐘同相以后,需要等待218個時鐘周期后會輸出有效鎖定信號,整體閉環仿真中控制電壓逐漸穩定,鎖相環進入動態平衡。

3 結論

文中描述了鎖相環的關鍵電路,相位鎖定檢測電路的設計與仿真,通過分析常用的相位鎖定檢測方法,根據設計實際提出了一種全定制的數字實現方案,可以實現1/18時鐘周期的精度檢測,保證了電路的可靠穩定工作,采用SMIC0.18μm CMOS混合信號工藝完成了電路的設計、仿真,結果表明該電路在2.5 Gbps時鐘數據恢復電路中可以穩定可靠地工作。

評論