基于FPGA的串行多階FIR濾波器設計

摘要 FIR濾波器的設計分為濾波器系數計算和濾波器結構的具體兩個部分。為說明使用FPGA實現FIR的靈活性,文中列舉了一個多階串行FIR濾波器實例,并給出主要的源代碼和相關模塊的時序和功能說明,最后使用Matlab和Quartusii聯合仿真驗證了FPGA硬濾波器工程的正確性。

關鍵詞 FPGA;FIR數字濾波器;Matlab;仿真

數字濾波器是用于過濾時間離散信號的數字系統,通過對抽樣數據進行數學處理達到頻域濾波的目的。根據單位沖激響應函數的時域特性可分為兩類:無限沖激響應(Infinite Impulse Response,IIR)濾波器和有限沖激響應(Finite Inpulse Response,FIR)濾波器。與IIR濾波器相比,FIR濾波器的實現是非遞歸的,較穩定;且FIR濾波器可獲得嚴格的線性相位特性。因此,應用領域較廣。

FIR濾波器具有成熟的結構,使用Matlab強大的功能使得本來繁重的計算工作變得輕松。在具體應用時,要根據工程當中信號的特點:采樣速率、信號帶寬等具體使用Matlab得到FIR濾波器系數。濾波器的結構實現可以使用PC軟件、單片機、微處理器、FPGA、通用DSP芯片。其需根據信號特性選擇。文中主要使用FPGA實現高速時鐘下的串行FIR濾波器結構,達到速度和邏輯資源情況下的最佳均衡。

1 FIR的特點

有限長單位沖激響應(FIR)濾波器的特點:(1)系統的單位沖激響應h(n)在有限個n值處不為零。(2)系統函數H(z)在|z|>0處收斂,極點全部在z=0處。(3)結構上主要是非遞歸結構,沒有輸出到輸入的反饋,但有些結構中也包含有反饋的遞歸部分。

設FIR濾波器的單位沖激響應h(n)為一個N點序列,0≤n≤N-1,則濾波器的系統函數為

![]()

即有N-1階極點在z=0處,有N-1個零點位于有限z平面的任何位置。

2 使用MatIab Fdatool設計FIR濾波器

FDATool(Fliter Design Analysis Tool)是Matlab信號處理工具箱專用的濾波器設計分析工具,操作簡單、靈活,可采用多種方法設計FIR和IIR濾波器。在Matlab命令窗口輸入FDATool后回車就會彈出FDATool界面。

帶通濾波器設計已知濾波器的階數n=1 024,beta=3.4。首先在Fiher Ttype中選擇Bandpass;在Design Method選項中選擇FIRWindow,接著在Window選項中選取Blackman—Harris;指定Filter Order項中的Specify Order為1 024;采樣頻率Fs=8 000 Hz,截止頻率Fc1=900 Hz,Fc2=1 200 Hz。設置完以后點擊窗口下方的Design Filter,在窗口上方就會看到所設計濾波器的幅頻響應,通過菜單選項Analysis還可看到濾波器的相頻響應、組延遲、脈沖響應、階躍響應、零極點配置等,如圖1所示。

這樣選擇File菜單當中的Export導出濾波器系數到文件中。因為得到系數是浮點數,為適合在FPGA中使用,要編寫一個M文件對系數進行整型量化處理并在此文件當中生成FPGA能夠使用的.mif表格文件。

3 FPGA設計和仿真驗證

當已知濾波器系數,信號速率為8 kHz,周期125μs。根據FIR濾波器的結構可知,只要在125μs之內完成1 024次乘加運算,那么就可達到對8 kHz速率的語音信號的有效濾波。文中使用QuartusII9.1開發平臺,FPGA芯片選用EP3C5E144C8,主時鐘25 MHz,周期40 ns進行1 024次運算,耗時40.96 μs125μs。

首先新建在QuartusII中新建一個工程FIR1024,然后使用原理圖和VHDL混合的方式設計出以下FPGA程序。把fircoef.mif表格文件代入到系數ROM存儲器中。

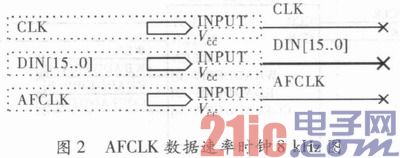

輸入管腳:CLK主時鐘25 MHz;DIN[15..0]語音數據輸入;AFCLK數據速率時鐘8 kHz;信號數據1 024點緩存RAM和濾波器系數ROM。

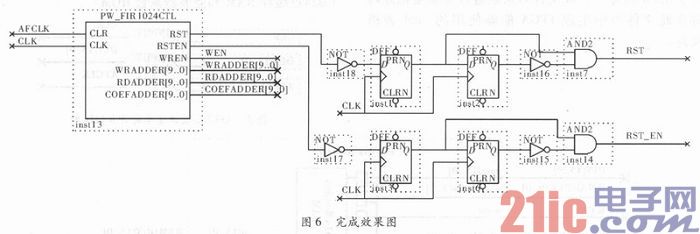

時序控制單元是設計的核心部分。AFCLK作為整個FIR濾波器系統的啟動信號,此模塊檢測到AFCLK上升沿到來時會進行以下幾個步驟的處理:(1)首先啟動WEN寫使能信號把當前DIN寫入緩存中,寫地址WRADDER累加一次。(2)然后啟動讀地址計數器RDADDER開始進行1 024次計數,同時把信號緩存和系數ROM中的數據送到乘加器中做1 024乘加運算,RST的作用是在第一個有效數據到來時進行累加器清零,RST_EN的作用是在完成1 024次運算時,準確地把結果鎖存到輸出端口,如圖6所示。

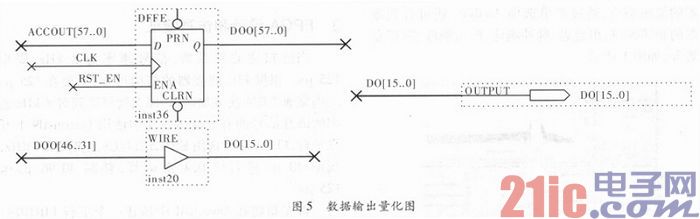

因為語音信號數據位寬是16位,經過1 024次乘加,和濾波器系數是32位整型量化處理的所有最終結果要做必要的量化處理,以得到正確的結果。

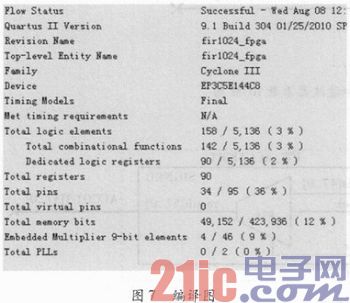

經過編譯綜合后,發現占用邏輯單元158,僅占EP3C5邏輯單元的3%,RAM單元約占12%,9位乘法器4個,如圖7所示,效果理想。

4 FPGA數字濾波器功能仿真驗證

QuartusII不支持Testbench,采用*.vwf文件進行仿真需要手工輸入激勵,人工檢查輸出結果,此程序反饋,且效率較低。由于Quartus II的工程文件都是文本文件,所有的數據都以文件形式存儲,所以可以編寫文本過濾程序,將文本文件中的有用數據提取出來,然后進行后期處理,既提高了靈活性,又提高了效率。

QuartusII支持*.vwf、*.vec等激勵輸入,由于*.vec的文本操作性優于*.vwf文件,所以文中選擇*.vec文件作為激勵輸入。使用Matlab產生8 000 Hz速率800 Hz,1000 Hz,1 300 Hz共3種頻率的混合信號的仿真樣本序列,帶入到QuartusII中進行仿真,產生的仿真文件再導出到Matlab中進行顯示,結果如圖8所示。

由圖中可以看出,經過FPGA濾波過后,800 Hz和1 300 Hz的信號都被濾波器濾除,僅有1 000 Hz信號保留。

5 結束語

通過設計實例,介紹了高速串行多階FIR濾波器的設計思路和流程。仿真結果說明,FPGA在FIR數字濾波器實現方面相比通用和專用DSP芯片具有更靈活的使用方法,可以做到速度和邏輯資源占用方面的均衡。

評論