對 Verilog 和 VHDL 說再見!

上周我跟我同事說,“ 兩種語言阻礙了嵌入式系統開發人員和軟件工程師借助Zynq SOCs來提升系統性能。”那就是“Verilog” 和 “VHDL”

本文引用地址:http://www.j9360.com/article/201610/308329.htm正如期待那樣,這已經得到了解決—因為SDSoC開發環境真的可以實現。

設計師不用學習更多新的工具來提升性能,或者選擇越來越快的處理器來代替現有芯片。使用Zynq SoCs 和Zynq UltraScale+ MPSoCs可以提升嵌入式系統性能一至二個數量級,并且可以減少BOM成本,使用可編程邏輯的特別系統分區,獨立的軟件和硬件開發流程。

現在,賽靈思推出SDSoC開發環境,它是為使用C/C++設計團隊特別設定的。基于Eclipse的SDSoC開發環境采用了業界首個“全系統優化的編譯器”來自動轉換C/C++為:

在Zynq器件中ARM處理器操作系統調用的面相對象的語言

片上邏輯上的硬件加速度器

用于ARM處理器和可編程邏輯之間交互數據的IP核

用于測試和分析性能的語言

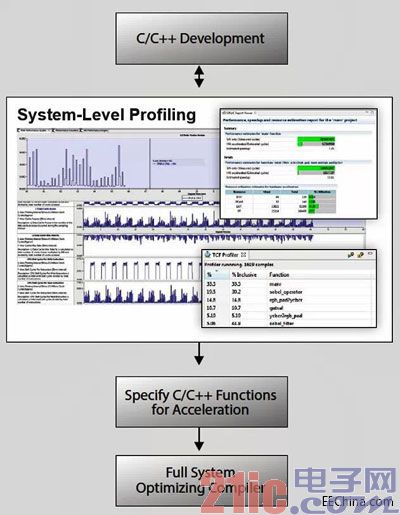

SDSoC的工作流程如下:

整個流程很像純軟件的嵌入式設計,但是它更快,這得益于可編程邏輯上的硬件加速器。

SDSoC開發環境利用片上邏輯資源創建軟件可用的硬件加速器,該片上資源是基于程序編譯指示,編程分析,計劃,硬件連接模式的連接。SDSoC使用特定的板級支持包(BSP)來創建

可編程邏輯部分

針對性的軟件加速功能

IP和經過優化的庫

自動生成的系統連接

然后全系統優化的編譯器自動將系統編譯為一個完整的軟件或者硬件系統。同時也會生成可編程邏輯比特流文件和用于ARM的ELF文件。

在此,盡管你沒有在上述流程上看到Verilog 或VHDL,這并不意味著賽靈思砍掉對HDL語言的支持。SDSoC開發環境會封裝和自動生成HDL、綜合、布局布線就像C/C++編譯器封裝和自動完成代碼優化和轉化為目標語言一樣。

SDSoC開發環境包含許多基于Zynq的開發板的支持包,包括ZC702,ZC706,賽靈思圖像處理開發板,以及第三方的安富利的Zedboard,Microzed和德致倫的ZYBO開發板。這些支持包(BSP)包含元數據使得SDSoC開發環境可以抽象化嵌入式平臺以提高生產效率和加速研發周期。

這里演示一個7分鐘例子來展示通過一個簡單的方法能夠在視頻Pipeline系統上提升60x速度的代碼執行過程。

SDSoC開發環境系統優化編譯器使用ARM和可編程邏輯在最短的時間內來實現系統任務。SDSoC使得系統架構師和軟件團隊使用“萬能的”C/C++來快速地實現片上資源的優化,自動生成系統連接以提高系統內部連接性能。嵌入式系統設計師可以權衡性能,數據吞吐量,延遲,同時縮短設計周期。

這可能不是你第一次碰到嵌入式自動化工具了,所以,你可能對此還是持有懷疑態度。但是,你必須知道SDSoC系統編譯器是基于賽靈思高層次綜合(HLS)編譯技術的,且這項技術已經有超過1000個開發人員使用。就是說,已經有許多人在你之前使用了SDSoC開發環境了。

SDSoC是SDx開發環境系列的第三款產品,這些產品帶來了顯著的性能提升和功耗降低,應用于廣泛的系統開發人員和軟件工程師,例如高速網絡(SDNet),數據中心應用(SDAccel),現在是嵌入式系統(SDSoC)。SDx開發環境提供非常簡單,類似于ASSP的開發流程,使你可以不用變成HDL專家也可以在可編程邏輯獲得性能上的提升。

評論