基于JTAG接口的內建修調電路的設計

摘要:為減小基準電壓源的誤差,提高集成電路精度,設計了一種基于JTAG接口的熔絲燒斷修調電路,著重分析JTAG接口及修調技術的具體實現。通過調整電路內部結構,使基準電壓在-40到85度的范圍內誤差不超過100ppm,并通過流片驗證了該設計的可行性。

本文引用地址:http://www.j9360.com/article/201610/308284.htm集成電路的工藝偏差問題是設計高精度電路的主要障礙之一,為提高芯片的合格率,引進修調技術已成為實現高精度集成電路的必要手段。目前,常用修調技術包括電阻薄膜激光修調、熔絲燒斷修調、二極管短路修調和內嵌非揮發性存儲單元的修調技術等。熔絲燒斷修調通常采用大電流將熔絲電阻燒斷,當修調開關少時,可引入額外的修調PAD并直接在PAD處燒寫,再使用譯碼器。但當修調開關多時,附加的PAD會占用較大的芯片面積,為減少附加引腳或修調PAD,可使用移位寄存器通過串行接口輸入數據并在芯片內部設計修調電路。為找到一組合適的開關碼并將其固定,電路需有移位搜索、燒寫及燒寫后讀值等工作模式。多重模式選擇勢必增加外部控制引腳,為減小芯片面積,決定采用JTAG接口來實現對串行輸入式熔絲燒斷修調電路的控制,通過TAP控制器及指令寄存器來控制修調模式選擇。本文給出了一種基于JTAG接口的內建修調電路的設計方法,此次設計采用華虹0.35umBCD工藝實現并進行了流片驗證,結果表明該電路完全實現了設計功能。

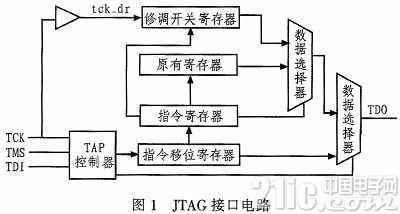

1 JTAG接口電路的設計

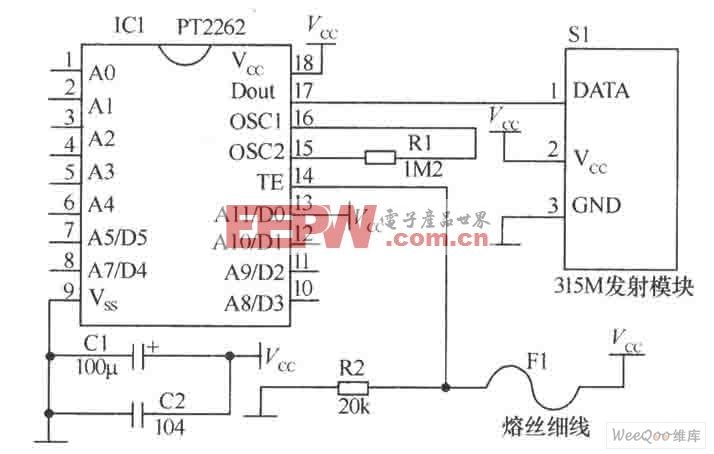

JTAG(Joint Test Action Group)聯合測試行動小組)是一種國際標準測試協議(IEEE 1149.1兼容),主要用于芯片內部測試。標準的JTAG接口是4線:TMS、TCK、TDI、TDO,分別為模式選擇、時鐘、數據輸入和數據輸出線。本設計所需的JTAG接口由以下幾部分組成:TAP控制器、指令寄存器及數據寄存器(這里指修調開關寄存器),可以從圖1中更直觀的看出。

1.1 TAP控制器的設計

TAP控制器是一個同步狀態機,把接收到的TMS和TCK信號譯碼,產生所需要的操作控制序列,控制電路進入相應的測試方式。設輸入為tms,輸出為state(即當前狀態),定義next_state為下一狀態。

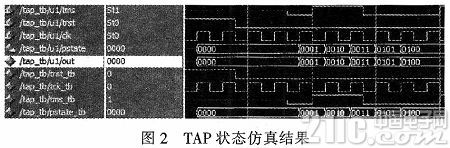

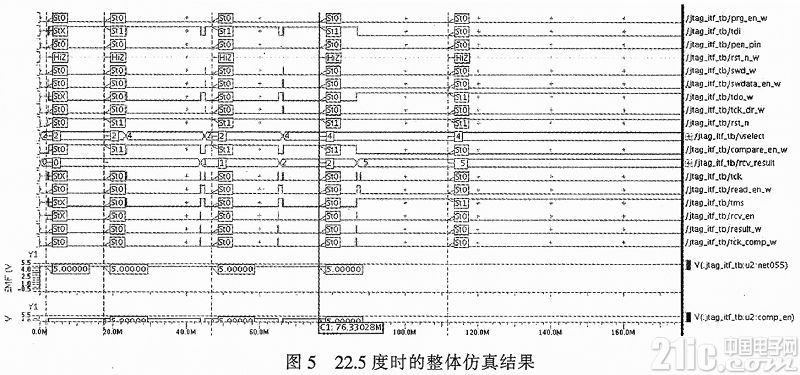

編寫程序及測試代碼,涵蓋所有TAP控制器的狀態,從圖2的仿真結果中可以看出,隨著時鐘變化,state的狀態在變化,TAP控制器的狀態按照如下順序變化:TEST_RESET,TEST_IDLE,SELECT_IR,CAPTURE_IR,SHIFT_IR,EXIT1_IR,UPDATA_IR,SELECT_DR,CAPTURE_DR,SHIFT_DR,EXIT1_DR,UPDATA_DR,SELECT_DR,SELECT_IR,TEST_IDLE,回到TEST_RESET狀態,與測試代碼一致。

1.2 指令寄存器

指令寄存器是JTAG模型結構的重要組成部分,其操作必須符合相關要求。本次通過取用指令寄存器的非公共指令部分定義新的指令用以控制修調電路的模式選擇,設計中指令寄存器實際上是兩個等長的寄存器,即移位寄存器和輸出寄存器。在SHIFT_IR狀態下,數據由TDI移入移位寄存器,在更新IR狀態下,數據由移位寄存器加載到輸出寄存器。目的是避免在移位過程中出現過渡數據影響系統功能。

1.3 數據寄存器

在本設計中需要用到一個修調開關寄存器,利用Spice軟件進行設計,具體設計見第3節。但在驗證JTAG接口功能時,需要模擬一個修調開關寄存器,給予這個假設的寄存器

相應的輸入信號。根據IEEE1149.4邊界掃描標準,測試邏輯結構中至少要有一個旁路寄存器(Bypass Register)。通常當芯片不在測試模式的狀態時則將JTAG配置為旁路模式。將這些數據寄存器置于公用的串行輸入(TDI)和串行輸出(TDO)之間,由指令寄存器控制掃描路徑。

2 修調電路的設計

本次設計的核心是16位熔絲燒斷修調控制電路,修調的對象是電壓值為2.5000V的帶隙基準,可應用于帶隙基準電壓源芯片或包含帶隙基準的系統級芯片內部。通過修調使得在-40到85度的溫度范圍內,在各工藝角下電壓與溫度關系的仿真結果為呈現出近似拋物線的形狀。

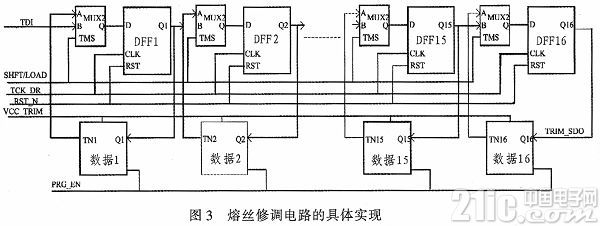

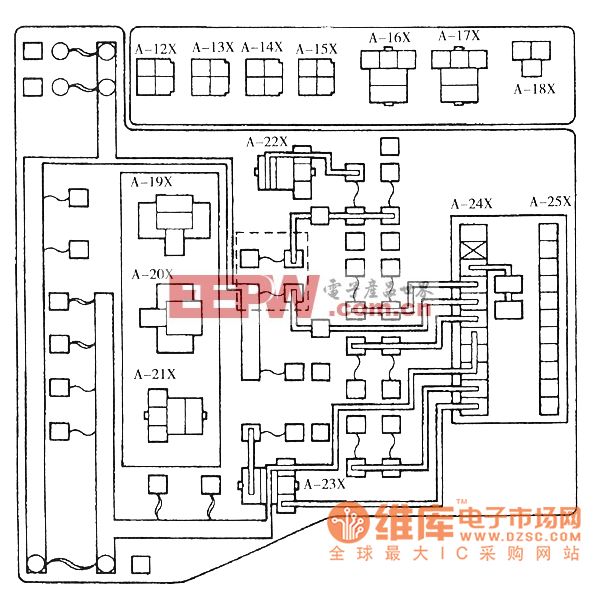

修調電路的總體結構如圖3所示;端口包括TCK_DR、RST_N、TDI、SHIFT/LOAD、VCC_TRIM以及PRG_EN。其中TCK_DR采用獨立時鐘以避免和TCK保持一致時,修調開關寄存器在不需要的情況下工作時移位和燒寫引起的偏差。端口SHIFT/LOAD是數據選擇器的選擇端,控制信號由LOAD指令譯碼產生,只有在TAP為CAPTURE_DR狀態且指令為READ_FUSE時為0,當指令為READ_FUSE且TAP狀態為SHIFT_DR時移位,此時TCK_DR是有效的。VCC_TRIM為燒寫電源,PRG_EN為燒寫使能。電路首先進入的是移位搜索模式,將數據送入修調寄存器內,搜索16個數字開關對應的值,只有在指令為LOAD_DS,且TAP狀態為SHIFT_DR時移位。之后進入燒寫模式,在燒寫控制端有效時(PRG_EN只有在指令為TRIM且TAP狀態為UPDATE_ IR時才為1),逐位依序進行燒寫(燒斷熔絲)。最后讓其進入燒寫結果讀出模式,從TRIM_SD0端讀出燒寫的結果,如果正確,電路則進入正常工作狀態。

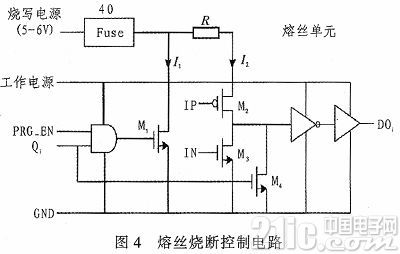

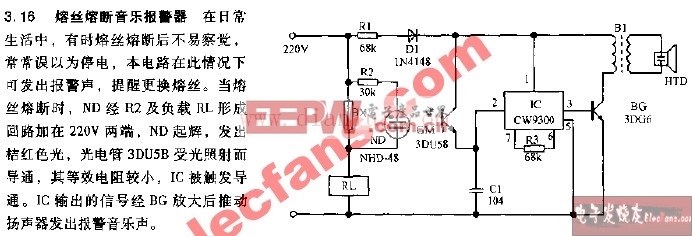

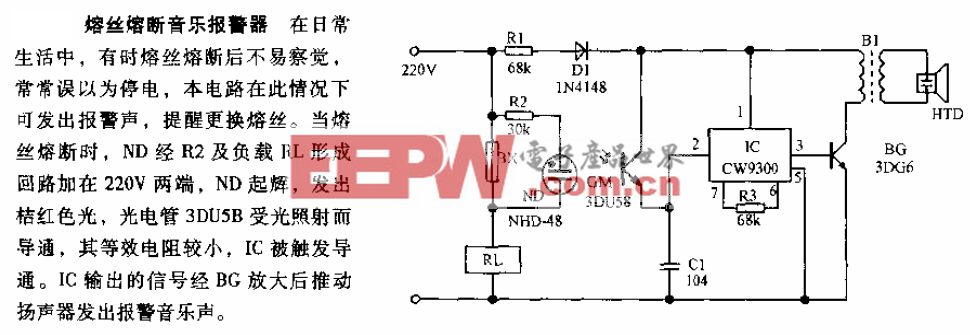

如圖4為熔絲燒斷控制電路。

本次采用的HHNEC工藝中的熔絲器件叫Fuse,是多晶材料做成的,初始電阻為40 Ω。當Fuse連入電路中時,通過計算熔絲燒斷過程中流過Fuse上的電流應為125 mA,并且燒寫使能需要持續5 ms的高電平才能燒斷。當燒寫控制端PRG_EN有效,且Qi為1時,M1管導通,此時電路中要流過相當大的電流。熔絲燒斷位所對應的二進制值為1,未燒斷則為0。

3 仿真驗證

整體功能的驗證是通過在虛擬機環境下運行AdvanceMS軟件進行混合仿真完成的。混仿的數字部分主要是JTAG模塊,模擬部分則通過Spice文件生成網表。在溫度為22.5度時,經過測試找到了一組滿足基準電壓要求的開關組合為0X7FC0。在-40和85度溫度下經驗證仿真結果與22.5度時的相同。

4 結論

本文基于華虹0.35 μm BCD工藝成功實現了一種基于JTAG接口的內建熔絲燒斷修調電路的設計。實現了外部控制器對電壓源內部電阻串結構的控制,通過改變電開關組合從而調整電壓值。利用ADMS軟件進行混合仿真調試,最后得到一組滿足要求的開關組合0X7FC0,在-40、22.5和85度下,誤差不超過0.000 2 V。此設計已應用在一種回路供電儀表專用芯片中,且芯片已流片成功,因此設計具有實際意義。

采用JTAG接口設計有效地減小了芯片面積,與激光修調相比,降低了設備費用成本,并且實現多個芯片同時測試及放入溫箱中同時進行修調,降低了芯片的修調時間,提高了工作效率。

評論