基于FPGA的數字通信實訓平臺的設計與實現

摘要:本實訓平臺著眼于提升高職層次學生的職業能力,圍繞典型的數字通信系統模型,設計了擴展性強、可測性好的FPGA核心板,并開發了多個配套的功能模塊。憑借著FPGA強大的硬件可編程能力,創設了分層遞進的實驗模式。學生通過逐步深入的實驗項目,牢牢掌握數字通信系統構成的基本要素,同時初步掌握實現現代通信產品的典型技術手段。

本文引用地址:http://www.j9360.com/article/201610/306473.htm通信系統的全面數字化是通信發展的必然趨勢。高職院校以《數字通信系統》替代《通信原理》符合行業的發展和企業對人才素質需求。作為電子信息類專業核心課程,由于課程內容抽象,理論較深,必須借助實驗環節來幫助學生理解。而傳統的通信原理實驗僅僅是對系統中單元模塊進行原理的驗證,學生無法在實驗中建立系統的概念,嚴重影響了后續專業課程的學習。

目前市場上的通信原理實驗箱大多以本科《通信原理》課程為設計藍本,主要開展單元電路的驗證性實驗。這顯然不能滿足高職層次的培養目標,難以推動學生的專業技能的提升。

本實訓平臺采用了模塊化設計,只需更換相應模塊,就可以完成不同的實驗。同時充分考慮到構建系統概念的重要性,在設計系統實驗時,學生需要掌握了最基本的通信系統組成要素,才能完成實驗,這對于強化學生的系統概念,起到了很大的作用。

1 平臺設計方案

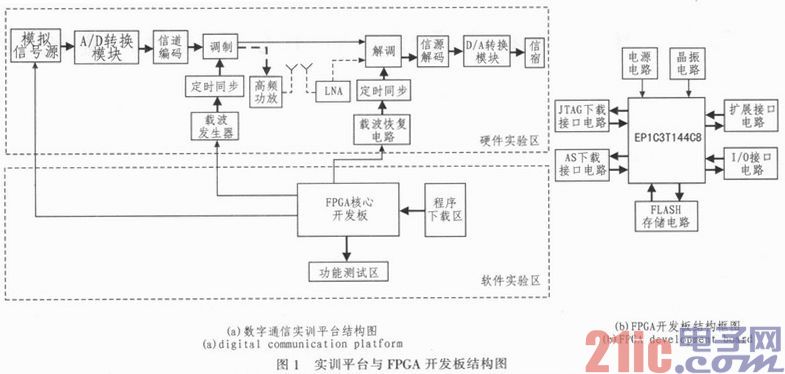

本數字通信實訓平臺將各個單元實驗模塊與數字通信系統的模型有機的結合到一起,并充分考慮到實際通信電路與傳統通信實驗電路的差別,設計了如圖1(a)所示的平臺結構。實訓平臺分為兩個部分:硬件實驗區和軟件實驗區。

1.1 硬件實驗區

根據數字通信系統模型,設計制作了FPGA核心開發板、信號源模塊、信源編碼模塊、信道編碼模塊、數字調制模塊、數字解調模塊、同步模塊、信源譯碼模塊、信道譯碼模塊。學生既可以通過完成各個單元電路的實驗,了解通信中重要的性能指標,又可以通過各單元模塊組成數字通信系統,熟悉構建通信系統的基本要素,強化系統概念。

1.2 軟件實驗區

基于FPGA核心開發板,首先為硬件區電路提供各種工作時鐘信號,其次學生可以通過VHDL語言編程實現各個實驗模塊的功能。在軟件實驗區,還設計了功能測試區,學生將軟件下載至核心開發板中,可以開展信號測試與軟件調試等相關實驗。最終,以FPGA開放模塊為核心,利用軟硬件平臺把相關模塊進行整合,將數字通信系統構建在一個芯片的內部。SOC(片上系統)是目前通信系統的最佳實現方案,讓學生初步建立SOC的基本概念并了解通信系統設計流程,有助于他們的職業發展。

2 系統硬件設計

實訓平臺的硬件設計充分考慮其實用性,易操作性以及與實際通信系統的結合度,并結合高職教育特點,采用了6+2的設計模式。其中“6”是實現數字通信的基本模塊:FPGA核心開發板、模擬信號發生模塊、信源編解碼模塊、信道編解碼模塊、數字調制與解調模塊、信號輸出模塊。“2”是兩個擴展模塊:無線數字通信發射模塊和無線數字通信接收模塊。限于篇幅原因,本文主要介紹FPGA核心開發板。

2.1 核心開發板功能

1)為硬件實驗區模塊提供時鐘信號、偽隨機序列等各種工作信號;

2)為軟件實驗提供開放的硬件平臺.使得實驗結果更加直觀;

3)開展電子設計開發和驗證.提升學生的綜合軟硬件設計創新能力。

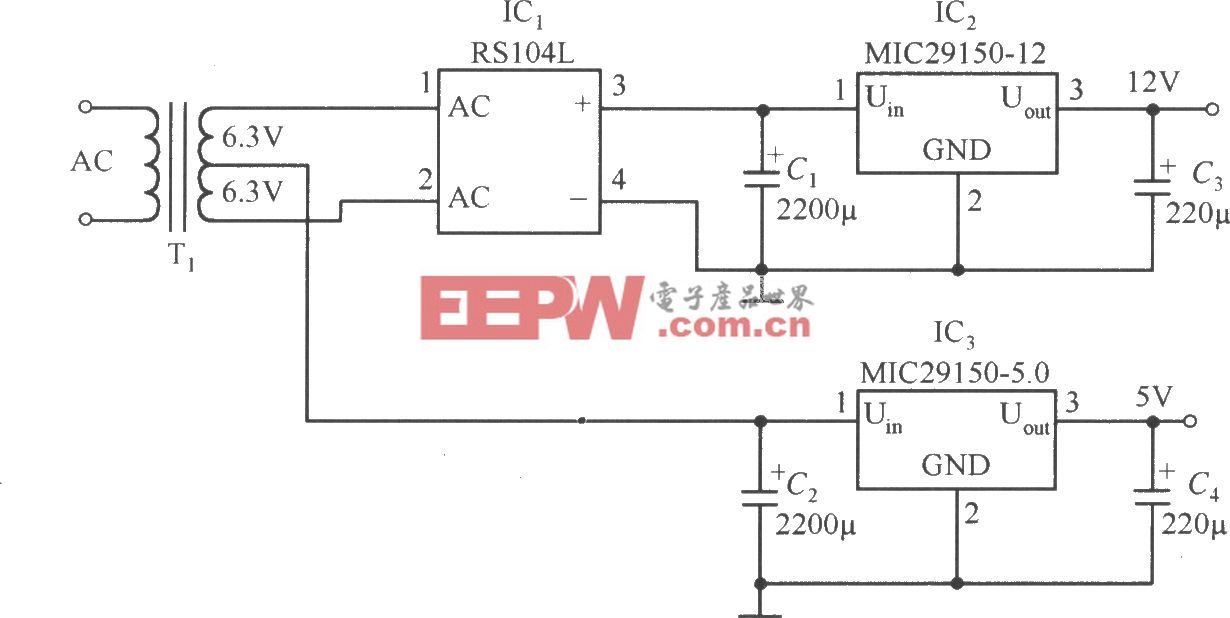

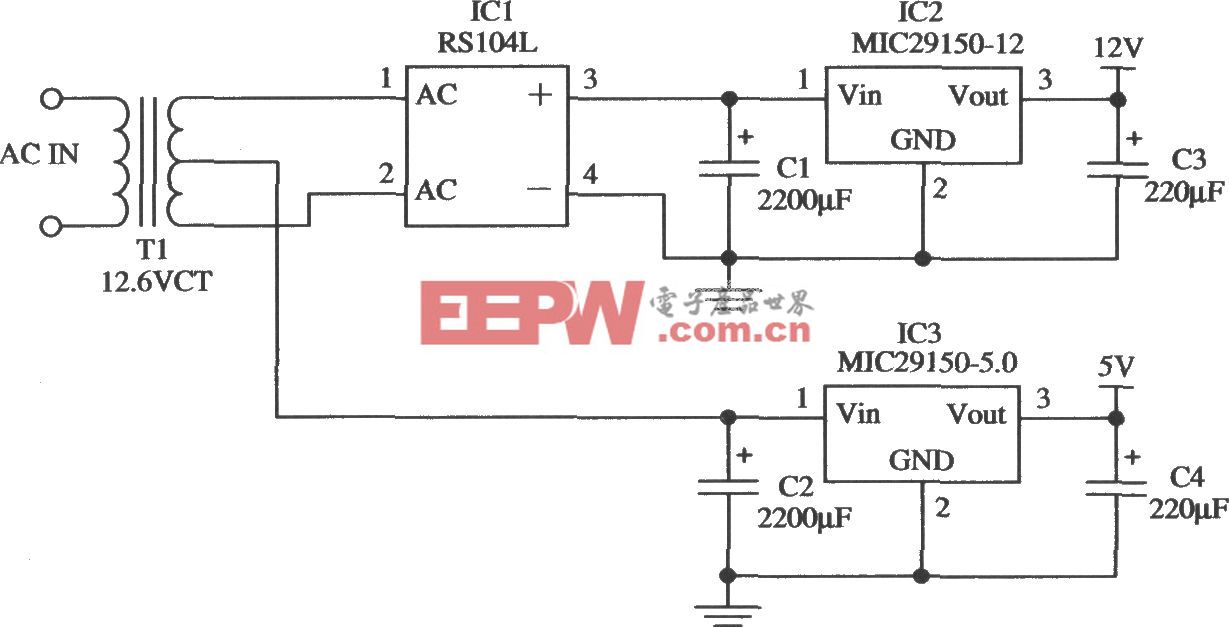

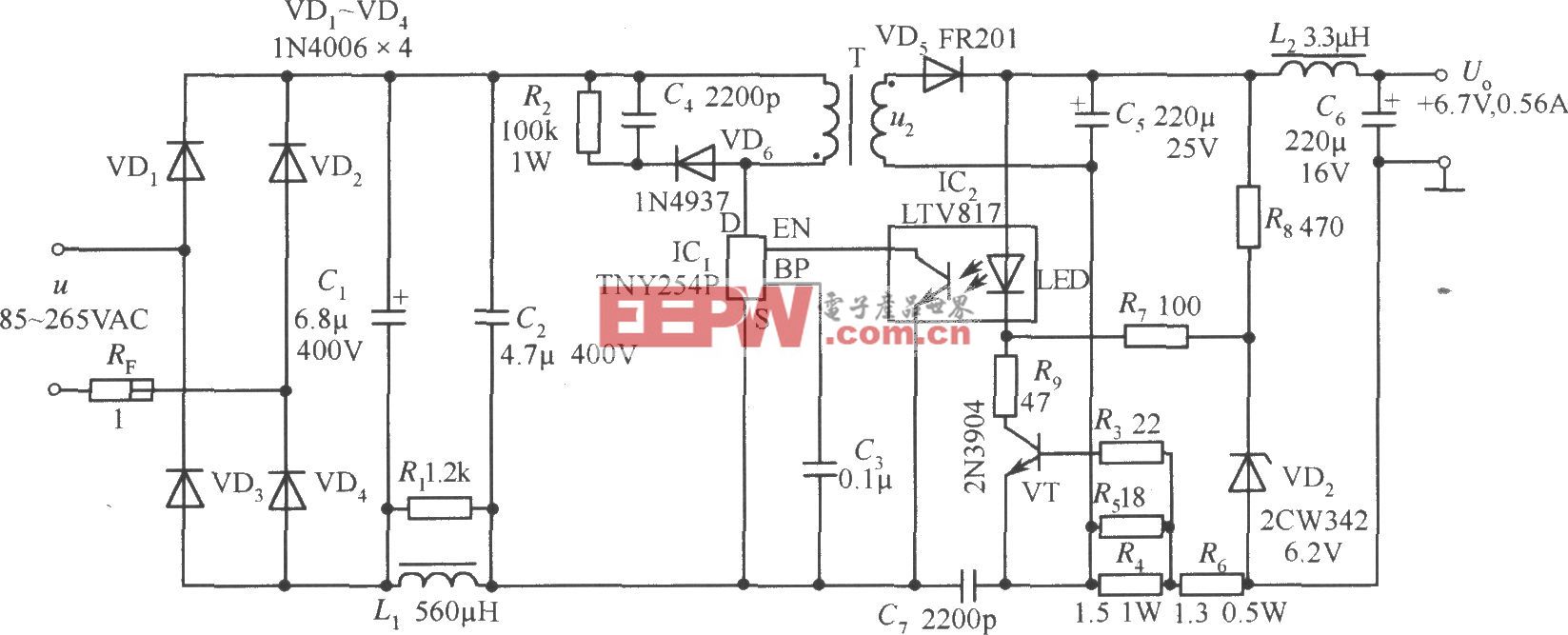

開發板電路包括:主芯片電路、晶振電路、電源電路、下載接口電路、擴展接口電路以及測試區電路。結構框圖如圖1(b)所示。

2.2 主芯片電路

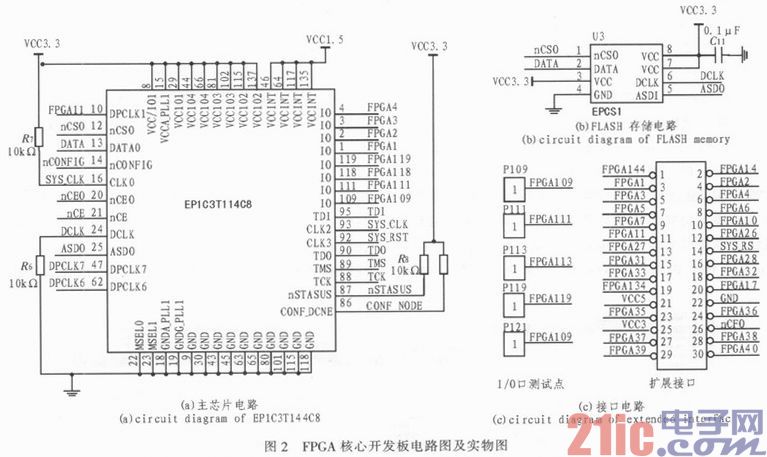

本設計選用Altera公司的Cyclone系列芯片,型號為EP1C3T144C8,該芯片是Altera公司推出的低價格、高容量的FPGA,在實際應用中被廣泛的采用。電路圖如圖2(a)所示。

2.3 FLASH存儲電路

由于FPGA芯片掉電后程序丟失,為保存程序數據,要在硬件上增添存儲電路。本設計采用標準串行配置器件EPCS1,存儲容量為1Mbit的FLASH存儲芯片。電路圖如圖2(b)所示。

2.4 I/O接口電路

為了加深學生對通信系統硬件電路工作過程的理解,將部分I/O口通過獨立測試孔的方式設計在開發板上。學生通過程序,將輸出信號設定在預留的I/O口,然后以導線連接的方法,將信號送至相關模塊的電路中。實物照片如圖2(c)所示。

2.5 擴展接口電路

擴展接口有2組15x2的排針,除了引出其余的I/O口,還將VCC、GND以及CLOCK等也設計在擴展接口。這為后續擴展外圍電路提供了極大的方便。其中VCC具有多種電壓,可以滿足不同器件的使用。電路圖如2(c)所示。

3 系統軟件設計

軟件設計采用QuartusⅡ9.0進行開發,設計分為兩個層次:一是主要實現時鐘信號產生、信源編譯碼模塊、信道編譯碼模塊以及數字調制解調等數字通信系統中單元電路的軟件功能;二是基于軟件無線電設計思路,通過Quartus自帶的SOPC Builder設計出貼合實際產品功能的可編程片上系統。

3.1 基本功能

以分頻模塊為核心,為基本實驗模塊提供必要的時鐘信號,學生可以通過編程改變時鐘信號頻率,改變電路工作狀態,從而加深對電路原理的理解以及實際電路調試步驟。

在設計軟件模塊時,還充分考慮相關模塊在通信系統中邏輯關系,通過軟件可將基本模塊進行連接,實現最簡化的數字通信系統。

3.2 系統模型設計

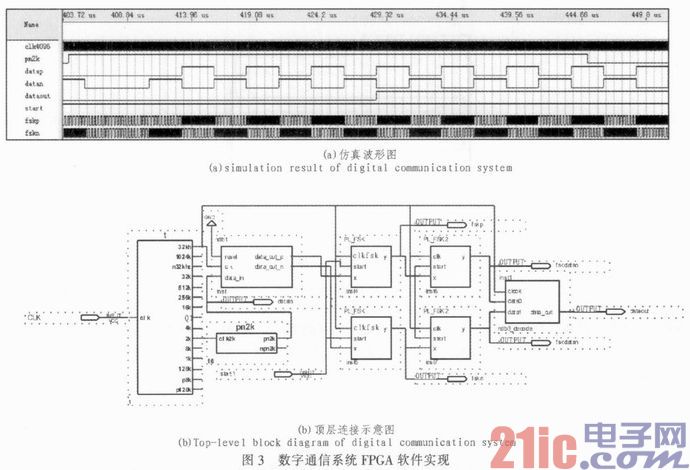

頂層連接圖如圖3(b)所示。FPGA開發板上的20 MHz有源晶振作為總的時鐘信號輸入,經過分頻模塊t分頻后可以產生多種頻率的時鐘信號,其中2 kHz作為輸入時鐘送入m序列模塊(pn2k),產生2n-1位PN序列,該序列作為數字基帶信號用于系統的信源輸入。

信道編譯碼選用HDB3碼編碼方式,將PN序列送至hdb1模塊中進行編碼,由于HDB3碼是一種雙極性碼,而QuartusⅡ軟件它無法識別-1,在它的波形仿真中只有1和0,因此這里采用了雙路輸出,其中datap中的高電平代表的是HDB3碼中的+1,datan的高電平代表HDB3碼中的-1,將兩路信號相減即可得到相應的HDB3碼。編碼模塊的時鐘信號為32 kHz,由分頻模塊提供。

兩路信道編碼信號datap和datan分別送入兩個數字調制模塊PL_FSK,本設計中采用了2FSK的調制方式,兩個載波由分頻模塊提供的1.024 MHz信號,分別經過12分頻和6分頻得到。其兩路已調信號輸出端口為fskp和fskn。

上述為發送端模塊的分析,下面簡單介紹接收端模塊的設計流程。

兩路已調信號fskp和fskn分別送入數字解調模塊PL_FSK2,設計思路是分別對已調信號和clk分頻信號進行計數,然后對兩個計數值進行判決,從而還原出兩路基帶信號fskdatap和fskdatan。

將fskdatap和fskdatan送入信道譯碼模塊hdb3_decode,根據HDB3碼的特點首先檢測出極性破壞點,即找出4連零碼中添加V碼的位置(破壞點位置),其次去掉添加的V碼,最后去掉4連零碼中添加的B碼以將其還原成NRZ碼PN序列dataout。

以上就是通過軟件實現基本數字通信系統的整個設計流程,仿真波形如圖3(a)所示。

其中,clk為系統輸入總時鐘,pn2k為數字基帶信號(偽隨機碼),start1為數字調制解調模塊使能信號,datap代表HDB3碼中+1的波形,datan代表HDB3碼中-1的波形,fskp為datap的FSK已調信號,fskn為datan的FSK已調信號,dataout為譯碼后的數字基帶信號(與pn2k一致,但有延遲)。

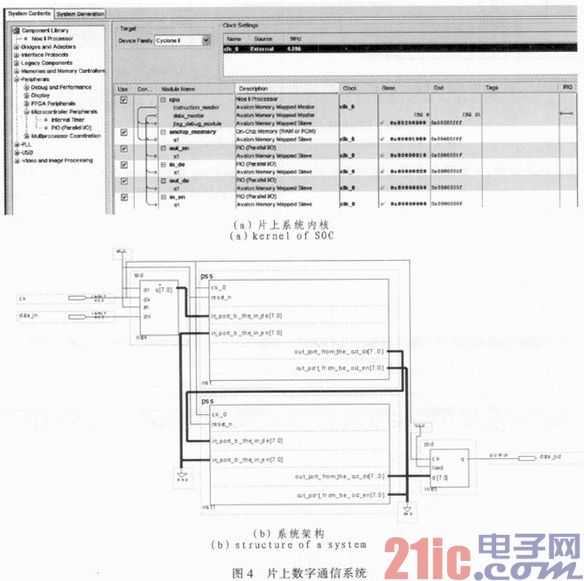

3.3 片上通信系統的設計

利用QuartusⅡ自帶的SOPC Builder可以較為簡單的設計出符合要求的可編程片上系統,以核心開發板上的晶振為基準時鐘,通過片內PLL可以進行分頻或倍頻操作。將編譯碼模塊與位同步模塊以及調制與解調模塊連通后,片上系統基本可以實現對高速數據準確、安全的發送和接收,片上系統CPU內核如圖4(a)所示,系統總體架構如圖4(b)所示。

4 系統實測

為保證高職層次的學生能夠更加直觀的了解掌握數字通信系統的相關概念,為后續專業技能培養奠定堅實的基礎。整個實訓平臺的實現圍繞著FPGA核心開發板,采用了分層遞進的實驗模式,逐步培養學生的相關專業技能。

4.1 采用硬件模塊搭接的方式構建系統

通過實訓平臺中各個單元模塊,按照數字通信系統的基本模型,進行輸入輸出信號的連接。FPGA核心開發板主要為各個模塊提供所需的時鐘信號、偽隨機碼等工作信號。學生在構建最簡化的數字通信系統過程中,一方面鞏固了通信系統的基礎知識,另一方面也鍛煉了學生FPGA軟件基本使用能力,為后續復雜程序編寫提供技術保障。

4.2 通過FPGA軟件實現通信系統模型

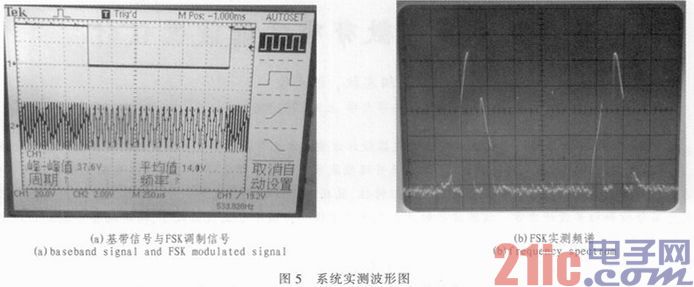

采用QuartusⅡ軟件,運用VHDL語言及圖形化編寫方式,按照通信系統模型及總體程序的需求,進行分模塊設計以及頂層連接。在設計軟件模塊時,對關鍵測試點進行芯片引腳設置,通過對核心開發板相關測試點進行實測,強化了學生對數字通信系統基本架構的認知,讓學生掌握測試儀器的基本使用方法。同時,進一步提升學生對于FPGA軟件編寫的能力。實測波形如圖5(a)(b)所示。

4.3 完成片上通信系統初步設計

隨著技術發展,當前數字通信系統已全部采用了片上系統的設計方式,以可編程的硬件為平臺,搭載特定的系統軟件,從而實現可靠高效的通信。由于該部分實驗具有一定的理論深度和技術難度,在具體教學實施中,選擇部分基礎扎實、動手能力強的學生進行SOPC片上系統設計實驗,強化實踐技能,提高他們的職業競爭力。

5 結束語

本實訓平臺從實際技能需求入手,貼合高職層次通信專業能力培養目標,把握數字通信系統中最核心的技術概念。采用硬件實測與軟件仿真相結合的實驗模式,既鞏固學生對核心技術的理解,又強化學生對通信系統基本構成要素的認知,同時也讓學生熟悉了現代通信系統典型的實現方法。

評論