基于JESD204協議的高速串行采集系統

摘要 在通信設施、成像設備、工業儀器儀表等需要大量數據的系統中,要求數據轉換級提供越來越寬的分辨率和越來越高的采樣率。并行接口的物理布局和串行LVDS方法的比特率限制,給設計人員帶來技術障礙。文中基于Xilinx Vertx6 FPGA的GTX高速串行接口實現了JESD204B協議,有效地解決了傳統采集數據并行傳輸時的各種問題。

本文引用地址:http://www.j9360.com/article/201610/306119.htm關鍵詞 高速串行接口;GTX;Xilinx VertX6;JESD204B

隨著轉換器分辨率和速度的提高,對更高效率接口的需求也隨之增長。JESD204接口可提供這種高效率,較之CMOS和LVDS接口產品在速度、尺寸和成本上更有優勢。采用JESD 204的設計具有更高的接口速率,能支持轉換器的更高采樣速率。此外,引腳數量的減少使得封裝尺寸更小且布線數量更少,這些都讓電路板更容易設計并且整體系統成本更低JESD204標準經過兩次更新,目前版本為B。由于該標準已為越來越多的轉換器供應商、用戶以及FPGA制造商所采納,它被細分并增加了新特性,提高了效率和實施的便利性。此標準既適用于模數轉換器(ADC)也適用于數模轉換器(DAC),還可以作為FPGA的通用接口。

1 JESD204協議

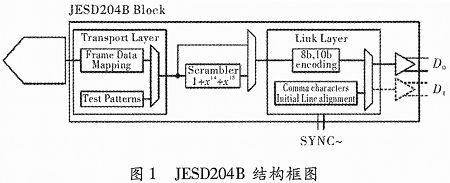

JESD204B協議體系結構可以分為物理層、鏈路層、傳輸層和應用層其結構原理框圖如圖1所示。

物理層實現高速串行信號的發送和接收完成數據串并、并串轉換以及編解碼處理。接口采用電流模式邏輯(CML)驅動器和接收器的差分對組成,通信速率定義在 312.5 Mbit ·s-1與3.125Gbit·s-1之間。差分電平定義為標稱800 mV峰峰值、共模電平范圍是0.72~1.23 V。該鏈路利用8h/10b編碼采用嵌入式時鐘。這樣便無須額外的時鐘線路,避免了高速速率下傳輸數據與額外的時鐘信號對齊的復雜性。鏈路層負責編碼幀數據。校驗數據,添加幀的邊界和流量控制。鏈路層只發送和接收幀,并不需要知道幀的內容。傳輸層的工作是將A/D采樣信息從數據流中提取出來。

2 JESD204B協議方案

2.1 Xilinx V6 FPGA

Virtex-6 FPGA是Xilinx公司推出的一塊高性能低功耗FPGA。其內嵌8~72個千兆位收發器GTX。每個GTX收發器都集成了發射器和接收器功能,能以 480 Mbit·s-1~6.6 Gbit·s-1的數據速率運行。通過采用基于FPGA邏輯的過采樣技術,可支持較低的數據速率。每個GTX收發器都有大量用戶定義的特性和參數,這些特性和參數可在器件配置器件定義,也有許多可以在運行過程中進行修改。GTX發射器實質上是一款并串轉換器,輸出使用單通道差分電流模式邏輯(CML)信號,TXOUTCLK是進行適當相處的串行數據時鐘,可直接作為來自內部邏輯的并行數據寄存器。輸入的并行數據由一個小型FIFO提供,可選擇使用 8b/10b、64b/66b算法對齊進行修改,以確保足夠數量的跳變。輸出信號擺幅可通以通過程序設定,其預加重也可編程從而補償印刷電路板的損耗和其他互聯特性。將輸入的位差分信號轉換為并行字流位寬可為8、10、16、20、32或40。可通過可編程均衡器,并使用FREF輸入對時鐘識別進行初始化,無須圖例的時鐘線路。數據模式采用不歸零(NRZ)編碼,可通過選定的編碼方案確保充分的數據跳變。隨后使用RXUSRCLK時鐘將并行數據傳輸到 FPGA邏輯中。

GTX接口眾多特性使其能夠方便地實現PCI—E、SATA、SAS等高速串行接口的物理層與鏈路層橋接。可以考慮使用GTX接口實現JESD204B協議,以正確解析JESD204B接口ADC轉化器發出的數據。

2.2 JESD204接口ADC轉換器

使用的ADC為TI公司生產的ADS42JB69,它是一款高線性、雙通道,16位,250 MSample·s-1的模數轉換器。該器件支持JESD204B串口,數據速率高達3.125 Gbit·s-1。經緩沖的模擬輸入在大幅降低采樣保持毛刺脈沖能量的同時,在寬頻率范圍內提供統一的輸入阻抗,這使得它可以輕松地將模擬輸入驅動至極高輸入頻率。采樣時鐘分頻器可實現更靈活的系統時鐘架構設計。此期間采用內部抖動算法以在寬輸入頻率范圍內提供出色的無雜散動態范圍(SFDR)。

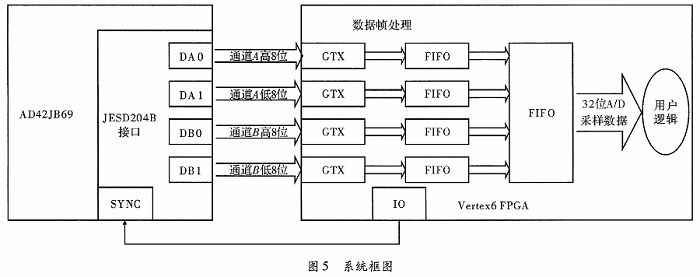

2.3 協議的實現

協議的實現是完成對AD42JB69的A/D采樣數據進行讀取。物理層完成了數據在線路上的傳輸,可以直接使用GTX與A/D相連實現。 A/D作為發送端FPGA作為接收端,鏈路層完成的主要功能是線路編碼和對控制字符的檢查。GTX接口內嵌了8b/10b編解碼模塊和控制字符檢測模塊,可以方便地實現與JESD204B標準設備的對接。在FPGA中基于GTX實現JESD204B協議,其難點主要有時鐘的配置,以及對協議據幀的解析。

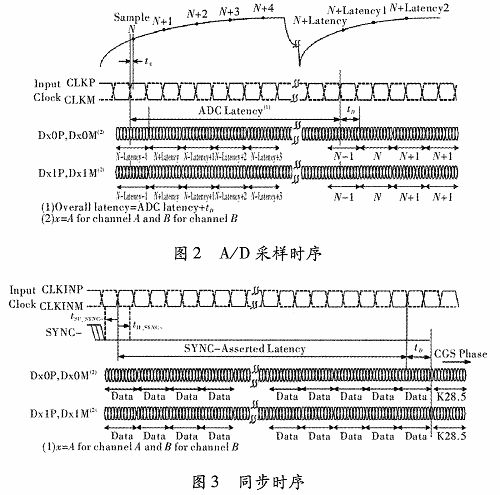

從時序圖可以看出,由A/D的采樣時刻到該時刻的采樣數據被FPGA接收到存在一個延時。

工程中需要滿足A/D采樣率200 MSample·s-1。AD42JB69的JESD204接口可以配置為四線模式和兩線模式。根據項目需求,應該使用四線模式才能達到200 MSample·s-1的采樣要求。在四線模式下A/D的數據映射關系如表2所示。其中DA0、DA1、DB0、DB1分別接4個GTX接口。傳輸兩個 A/D轉換器采樣數據的高8位和低8位。因為采樣時鐘與傳輸時鐘一致,JESD204設備先將A/D采樣的數據進行8b/10b編碼然后用與采樣頻率相同的時鐘將編碼后的數據進行并串轉換并發送給接收端。計算可得到發送線速度為2.0 Gbit·s-1。因此FPGA需要正確配置RXPLL_DIVSEL_REF、RXPLL_DIVSEL45_FB、TXPLL_DIVSEL_FB、 TXPLL_DIVSEL_OUT的值使GTX接收線速度能穩定工作在2.0 Gbit·s-1。

2.4 數據幀解析的實現

在串行數據收發過程中如何判斷數據的邊界尤為關鍵,JESD204協議采用字同步和幀同步解決數據邊界問題。通過在數據流中插入控制字符完成字同步和幀同步。以下列出JESD204B中使用的控制字符以及他們的功能。FPGA通過對控制字符的正確解析可以完成時鐘恢復、數據邊界認定,對齊等。

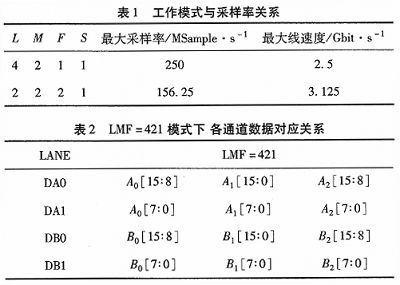

/K/=/K28.5/控制字符用來完成字同步。接收端可以通過拉低

使發送端持續發送/K28.5/控制字。當接收端接收到連續的4個/K28.5/字符后字同步建立。此時FPGA作為接收端已經完成了時鐘恢復,Comma字符檢測。字同步建立以后進行幀邊界確定。接收端拉高

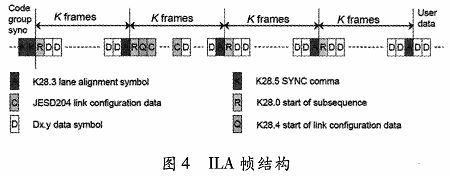

后發送端停止發送/K/28.5/控制字,開始發送ILA幀。ILA幀的結構如圖4所示,每個ILA幀包含4個多幀(Multi—Frame)。

/R/=/K28.0/做為每個多幀(Multi—Frame)的開始標志。

/A/=/K28.3/用于串行數據流中的多幀(Multi—Frame)同步。作為多幀(Multi—Frame)的結束標志。

/F/=/K28.7/用于串行數據流中的幀(Frame)同步,當當前幀的最后一個8位字節(Octet)等于前一幀的最后一個8位字節(Octet)時用/F/=/K28.7/控制字替換當前幀的最后一個字節。

通過上述規則檢測K字符并將A/D采樣數據存入FIFO。當完成了控制字符檢測后需要將A/D的采樣數據進行拼接,因為每路A/D轉換器都是以高低字節分開的方式傳輸數據的,因此要嚴格保證采樣時鐘的同步。系統使用兩級FIFO來對A/D采樣數據進行緩存。第一級4個FIFO完成采樣數據高低字節的同步,其存儲深度為16 Byte,4個FIFO的時鐘分別接4個GTX的RXUSRCLK,當FIFO存儲數據達到10時開始讀出數據,這樣就能保證4個FIFO的輸出由一個時鐘同步。第二級FIFO作為數據緩存,為用戶邏輯提供簡單接口,深度為4 kByte。用戶邏輯接口有RD_CLK,RD_READY。當FIFO存儲深度達到4 000時RD_READY信號拉高。可以通過判斷該信號開始讀取數據。RD_CLK需要>200 MHz,每次讀取4 kByte數據后再等待RD_READY信號有效,這樣循環就可以將A/D采樣數據連續地讀入到用戶邏輯。

3 實驗分析

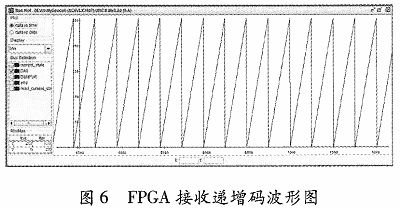

AD42JB69中包含了22個8位控制寄存器可以使用SPI接口對芯片的工作方式進行靈活的配置。可以配置芯片輸出遞增碼、隨機碼、零 -交錯碼、正弦信號等多種測試碼源。這些測試碼源可以用于驗證接口傳輸數據的正確性,實驗選用遞增碼作為測試碼源方便發現錯誤,圖6所示為使用 Chipscope觀察FPGA接收到的遞增碼波形。

4 結束語

隨著傳送速率的不斷提高,并行傳輸技術中的同步碼串擾等問題越來越嚴重,已不能滿足高速數據傳輸的要求,成為工程應用瓶頸。筆者在分析FPGA中高速串行收發器CTX功能和JESD204協議后。實現了一種A/D采集數據的串行傳輸方式,解決了并行傳輸中遇到的問題。用Verilog語言編寫了 JESD204協議控制核,節省了工程成本。

評論