高速信號采集記錄儀設計

摘要:針對高速信號實時采集存儲的需求,設計了一種高速信號采集記錄儀。記錄儀通過高速A/D轉換器對信號進行采樣,并實時存入NAND FLASH存儲陣列中。為提高數據存儲速率,綜合采用并行總線、交錯雙平面頁編程、多級流水線等技術,大幅提升FLASH的寫入速度。記錄儀可實現8bit、200MSPS的采樣速率,并可將速率為200MB/s的采樣數據實時存儲。

本文引用地址:http://www.j9360.com/article/201610/306117.htm0 引言

目前在各工業領域對數據采集存儲的需求越來越多,對采集速率和存儲速率的要求也越來越高。特別是在航空航天領域,經常要對高速信號進行采集,并將采集數據實時存儲在非易失存儲器之中,以便事后分析處理。

為滿足需求,本文提出一種高速信號采集記錄儀的設計方法。采用高速A/D轉換器對輸入信號進行200MSPS的高速采樣,然后將采樣數據實時存入 FLASH存儲陣列中。綜合采用了并行總線、交錯雙平面頁編程、多級流水線等技術,大幅提升FLASH的寫入速度,從而實現200MB/s采樣數據的實時存儲記錄。

1 系統組成及工作原理

1.1 記錄儀系統組成

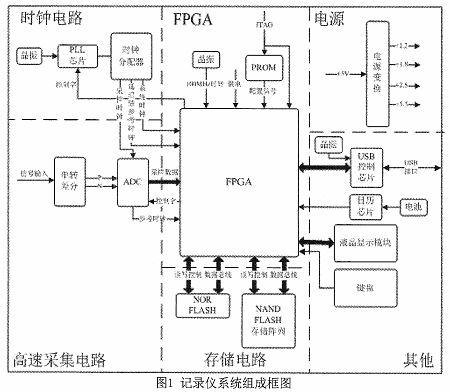

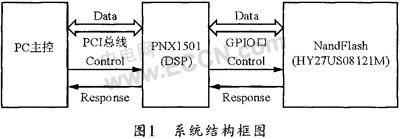

圖1為記錄儀系統組成框圖,記錄儀電路系統主要由FPGA電路、時鐘電路、高速采集電路、高速存儲電路、電源電路、其他外圍電路等組成。

PGA選用Xilinx公司的XC4VSX55,PLL時鐘芯片選用TI公司CDCF5801A,A/D轉換器選用TI公司ADS5547,NAND FLASH存儲芯片選用三星公司K9WAG08U1A,USB控制芯片選用CYPR ESS公司CY7C68013A。

1. 2 記錄儀工作原理

系統的工作原理為:上電后,FPGA首先讀取NOR FLASH中存儲的NAND FLASH壞塊信息,在內部RAM中建立壞塊表,之后每次需要對NAND FLASH進行讀寫操作之前,都要先查詢壞塊表,若準備操作的塊為壞塊,則跳到下一塊繼續查詢,直到找到好塊才進行操作。

當需要采集記錄信號時,先通過外接的鍵盤和LCD顯示模塊設置采樣參數。然后記錄儀接收到啟動信號后開始進行采樣記錄,需采樣信號從SMA接口輸入后經過差分放大器轉換為差分信號,然后進入A/D轉換器進行200MSPS采樣,FPGA接收采樣數據,采樣4級流水線對NAND FLASH存儲陣列進行寫入操作。此外FPGA還需完成對其他外圍器件的控制。

當需要上傳數據時,FPGA將數據從NAND FLASH中讀出,通過USB控制芯片將數據上傳給上位機。

2 關鍵技術

2.1 高速A/D采樣

記錄儀采用的A/D轉換器為TI公司的14bit、210MSPS的高速A/D芯片ADS5547。系統中實際采用的采樣時鐘頻率為200MHz,由50MHz晶振時鐘通過CDCF5801A倍頻產生。

ADS5547采用的工作模式為LVDS DDR模式,即在A/D輸出時鐘的下降沿傳輸采樣數據的奇位,在上升沿傳輸采樣數據的偶位,所以實際數據傳輸頻率為400MHz,對于這種高速數據傳輸,在PCB設計時需注意7對差分數據線和1對差分時鐘線保持等長,確保跡線傳輸延時相同。

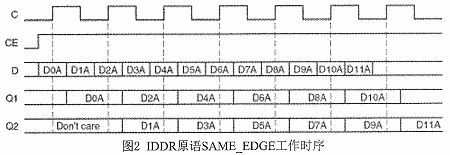

在FPGA數據接收模塊的設計中,直接調用芯片中的IDDR原語,如圖2所示,其在SAME EDGE工作模式下的時序正好匹配ADS5547的數據輸出時序,所以可將7路DDR數據轉換為14bit并行數據,考慮到NAND FLASH的寫入速度,在存儲時截取采樣數據的高8位,這樣需要存儲數據的速率為200MR/s。

2.2 高速數據存儲

記錄儀采用的非易失存儲器為三星公司的NANDFLASH芯片K9WAG8U1A,單片容量為2GB。由于單片FLASH的存儲容量和寫入速度有限,所以使用了16片FLASH成存儲陣列,總容量為32GB,并綜合采用了并行總線、交錯雙平面頁編程、多級流水線等技術提升寫入速度。

(1)并行總線

為了提升數據吞吐量,將N片FLASH芯片的I/O并行操作,總線寬度增加為單片的N倍,并共用讀寫控制線,這樣可將N片FLASH當做一片大位寬 FLASH同時進行讀寫操作,從而可以將寫入速度提升至N倍。在該記錄儀中,是將8片FLASH的I/O并行操作,每片FLASH的數據位寬為8bit,所以總位寬為64bit,寫入速率可提高為單片的8倍。平均數據寫入周期只需達到40ns即可實現200MB/s的數據速率,滿足FLASH的25ns最小寫入周期要求。

(2)交錯雙平面頁編程

NAND FLASH的寫入操作是以頁為單位進行的,稱為頁編程操作,分為兩階段進行。第一階段為數據載入階段,是將數據先寫入到頁寄存器中,第二階段為編程階段,是將數據從頁寄存器中真正編程到FLASH的存儲單元之中。數據載入頁寄存器時最高速率可達到40MB/s(單片),但數據編程階段所需時間為 200~700μs,若等待一頁編程完成之后再進行下一頁數據的載入會嚴重降低數據寫入速率。為充分利用編程階段的時間,并且增加數據載入時間以便于流水線操作,采用了交錯雙平面頁編程方法。

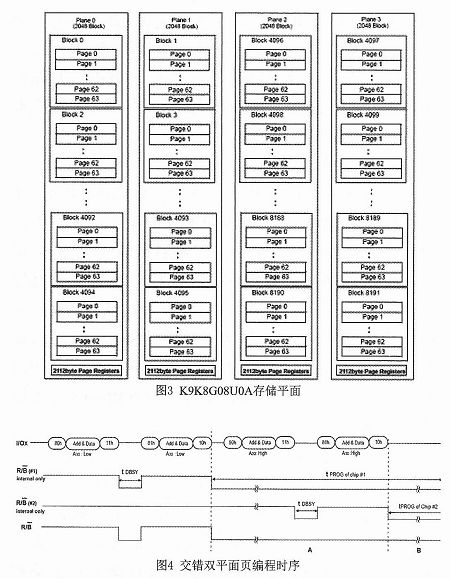

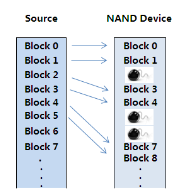

每片K9WAG08U1A實際上是由2片K9K8G08U0A組成,而每片K9K8G08U0A又由2片K9F4G08U0A組成,每片 K9F4G08U0A又由2個2Gb的存儲平面組成,每個存儲平面有獨立的2112字節頁寄存器,因此可實現雙平面頁編程操作,而2片 K9F4G08U0A之間可以實現交替操作。K9K8G08U0A存儲平面如圖3所示,Plane0和Plane1組成第1片 K9F4G08U0A,Plane2和Plane3組成第2片K9F4G08U0A。

當進行FLASH編程操作時,先發送雙平面編程指令,然后Plane0和Plane1進行數據載入,載入完成后進入編程階段。此時無需等待編程結束,直接對Plane2和Plane3繼續進行數據載入,即可實現交錯雙平面頁編程。操作時序如圖4所示。

(3)多級流水線

運用交錯雙平面頁編程方式后,可以連續進行4頁的數據載入操作,但載入完成后整片K9WAG08U1A的4個平面都將進入編程階段,無法繼續進行操作。為了實現數據的連續載入,采用了多級流水線技術。

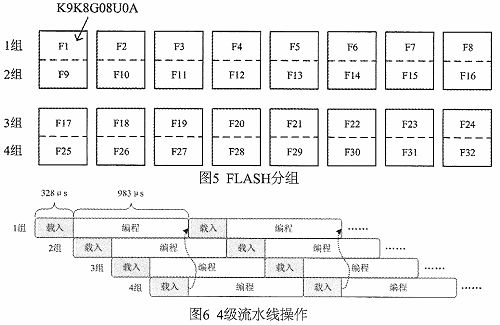

實現流水線操作首先要對FLASH存儲陣列進行分組。由于每片FLASH是由2片K9K8G08U0A組成,所以存儲陣列可以看作由32片K9K8G08U0A組成,把每8片K9K8G08U0A分為一組,在讀寫時并行操作,這樣整個存儲陣列分為四組,如圖5所示。

流水線操作方法如圖6所示。FLASH進行寫入時,首先通過片選信號選中第1組FLASH,進行數據載入操作,載入完成后,該組FLASH進入編程階段,此時切換片選信號,選中第2組FLASH,繼續進行數據載入,依此類推。由于采用了交錯雙平面頁編程方式,所以每個載入過程可以載入4頁的數據,而采用并行總線之后,位寬為64bit,即每個寫周期可寫入8Bytes的數據,按照200MB/s的數據速率計算,每個載入階段的時間為:

當第4組FLASH的載入過程完成后,距離第1組FLASH開始編程時已過去983μs,大于最長編程時間700μs,所以第1組可繼續開始數據載入操作。通過流水線操作,實現了數據的連續載入,從而大幅提高了寫入速度,實現了200MB/s的數據存儲速率。

3 試驗驗證

為驗證記錄儀的性能,進行了數據采集試驗。試驗中采用信號發生器產生周期為100ns的正弦信號輸入記錄儀,記錄儀對其進行實時采集存儲,采集時間為 5s,即產生的數據量為1GB。采集完成后,在上位機軟件中發出上傳指令讀取FLASH中的數據,并通過USB接口上傳到上位機形成二進制數據文件。然后截取其中的一段波形進行顯示,如圖7所示。

在圖中可以看到,正弦信號的每個周期對應20個點,而采樣周期為5ns,所以20個點為100ns,與設置的信號周期相一致,說明記錄儀實現了200MSPS的采樣速率和200MB/s的數據存儲速率。

4 結論

設計了一種高速信號采集記錄儀,該記錄儀可 實現8bit,200MSPS的采樣率,并可對采樣數據實時存儲。其電路系統可由單板實現,具有體積小,便于攜帶和應用的優點。該記錄儀適用于各種需要高速信號采集的場合,應用前景廣泛。

評論