星載計算機雙冗余CAN總線模塊設計與實現

摘要:隨著新型SoC(System On a Chip)集成技術在航天技術中的應用越來越廣泛,傳統的星載板級設計轉為SoC芯片級設計逐漸成為趨勢。基于IP—cores(the integration of complex building blocks)復用的SoC技術,是衛星研制中降低設計時間和成本行之有效的方法。本文以商用器件SmartFusion2為平臺,以CAN總線數據采集系統為例,闡述了CAN總線模塊的冗余架構設計和IP核復用技術,此方案不僅滿足了星載計算機平臺高集成度、低功耗、也提高了星載通訊網絡的穩定性和可靠性。

本文引用地址:http://www.j9360.com/article/201610/306099.htm隨著電子技術的進步和芯片集成化技術的發展,衛星平臺電子設備呈現小型化、集約化、智能化的發展趨勢。SoC(System On a Chip)作為一種新的系統集成技術,可以將一個單板系統甚至整個控制系統的功能集成在一塊芯片中實現,不僅可以提高星載電子設備集成度,減小體積重量,提高功能密度,而且可以提高性能和系統的總體可靠。

本文采用基于Flash為基礎的SmartFusion2系列FPGA芯片作為星載計算機平臺,該芯片將可配置模擬部件、大容量Flash內存構件、全面的時鐘生成和管理電路,以及基于Flash的高性能可編程邏輯模塊集成在單片器件中。與此同時,FPGA內部集成了高效的ARM內核——Cortex— M3,可以直接替換傳統的MCU+FPGA組合。

1 系統綜述

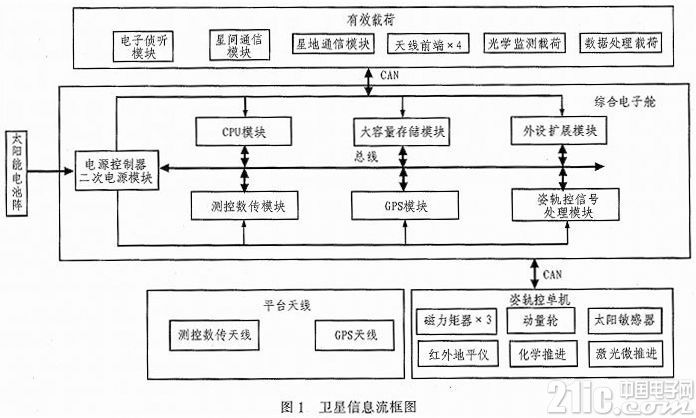

星載計算機作為衛星平臺的核心部件,采用總線網絡與星載其他電子設備進行互連通信,實現對衛星的多模塊控制、星上資源的優化與重組、整星綜合信息處理等工作。本系統采用CAN總線將各個單機模塊連接在一起,構建一個可以有效的支持分布式控制的串行通信網絡。

綜合電子艙內部集成了多個模塊,以Cortex—m3微控制器作為主控制單元,各單機模塊傳送的數據通過特定的通信接口將控制信號送給星載計算機微控制器模塊,并進行統一的數據處理與任務調度。系統平臺包含大容量存儲管理單元模塊,大容量存儲管理單元由獨立的處理器接受載荷的數據并存儲到4G bits的flash,根據中央處理單元的要求對大容量存儲單元進行操作,為存儲載荷的有效數據提供了保障。

衛星系統功能與信息流如圖1所示。

2 硬件設計

2.1 微控制器模塊設計

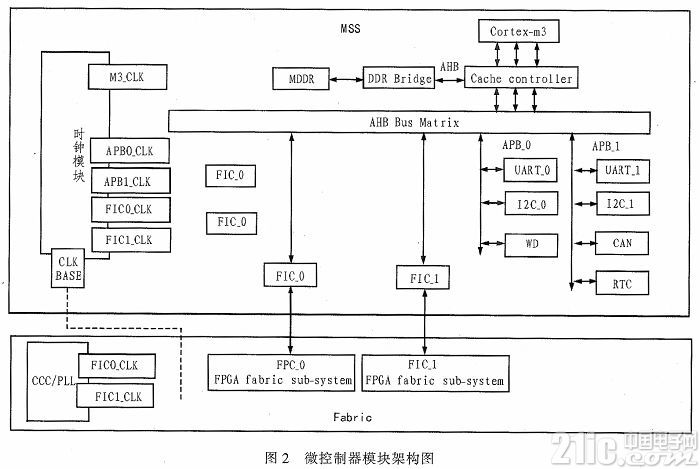

微控制器模塊是綜合電子艙的核心模塊,主要負責集中完成星上的數據處理、衛星飛行控制任務和姿態軌道數據處理等。基于商用器件SmartFusion2為平臺的星載計算機,集成FPGA、ARM Cortex—M3處理器硬核,以及可編程模擬資源于一體的器件,能夠實現完全可定制系統設計和IP保護能力,而且便于實現軟硬件協同設計。FPGA模塊提供的資源如圖2所示,主要包括:500000邏輯門單元,大于1 Mbit的RAM模塊,可用I/O引腳數大于300個。FPGA內嵌的處理器內核是Cortex-M3,主頻為166 MHZ,支持的外設有10/100/Mbps的網絡,USB2.0接口、CAN2.0控制器接口、UART串行調試接口等。存儲單元主要存儲系統的應用程序代碼及記錄數據,由NOR FLASH存儲器和DDRSDRAM組成。主內存是系統運行時代碼執行的區域,也是應用程序臨時變量和中間數據的存放空間,它的讀寫速度直接影響到了系統的計算效率,因此需要盡量提高主內存的訪問速度和空間大小。本系統中使用DDR SDRAM作為系統的主內存,保證內存訪問時間和內存容量不會成為影響系統性能的瓶頸。

2.2 CAN模塊設計

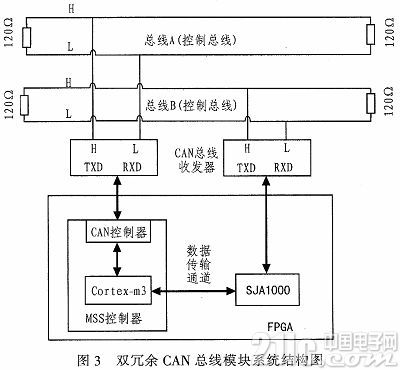

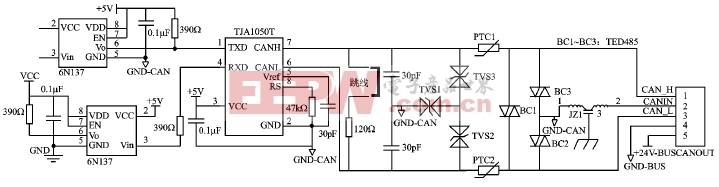

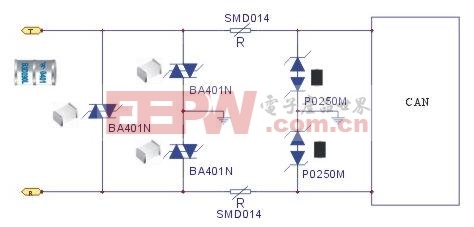

由于星載計算機本身處在惡劣的工作環境,在系統設計開發時必須首要考慮其本身的可靠性及容錯能力,所以為保證通信接口的可靠性,本系統采用冗余備份模式設計CAN接口模塊。硬件邏輯結構如圖3所示,CAN總線冗余設計采用控制器冗余模式,由兩個CAN收發器、兩個CAN控制器和單CPU組成。兩條數據通道完全獨立、互不影響。與此同時,雙CAN模塊采用熱備份工作模式,主用設備和備用設備同時處于上電運行狀態,且同步進行數據采集、數據處理和計算。但是備份設備的數據處理不起作用,僅當主用設備失效時,CPU才會選擇快速響應備用設備的中斷,并接收備用設備的數據。

2.3 CAN總線冗余模塊設計

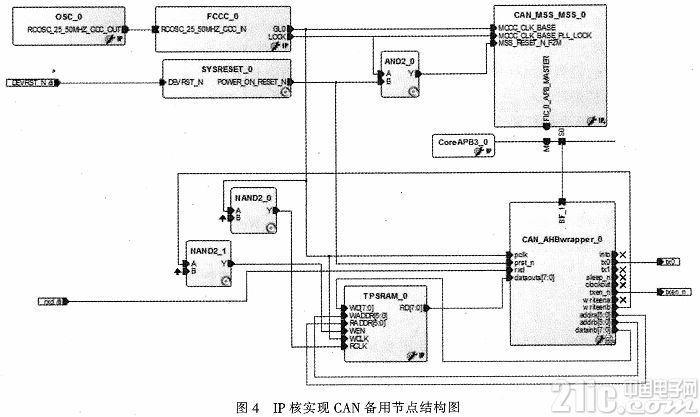

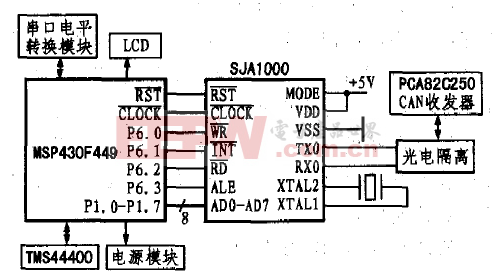

基于SmartFusion2的SoC設計平臺僅在APB_1總線上掛載了單一CAN2.0控制接口,為實現硬件冗余設計,利用了SoC提供的FPGA可編程邏輯資源實現了獨立的SJA1000CAN控制器。

如圖4所示,由VHDL語言設計實現SJA1000 CAN IP軟核的設計并生成系統可配置的動態模塊,主控單元Cortex—M3通過高級外設總線(APB3)總線接口將數據輸出,CAN總線控制器經過一個SRAM(報文緩沖器)與從設備實現通信并對數據報文進行預處理。

HDL程序在Libero IDE集成環境中完成,使用VHDL硬件描述語言編寫代碼,并編寫相關的測試代碼進行功能驗證。

3 軟件設計

CAN總線控制器的功能配置和行為由主控制器Cortex—M3設置的C程序完成,在SoftConsole集成開發環境中完成。

根據SJA1000設計的CAN控制器和微控制器自帶的CAN控制器構成了CAN總線上的雙冗余備份模式。兩者在內存中的映射起始地址分別為:0x40015000u和0x70000000u。由于兩種CAN控制器的IP核不同,需要根據每個控制器采用的協議設計CAN設備的驅動程序。

1)單節點驅動設計

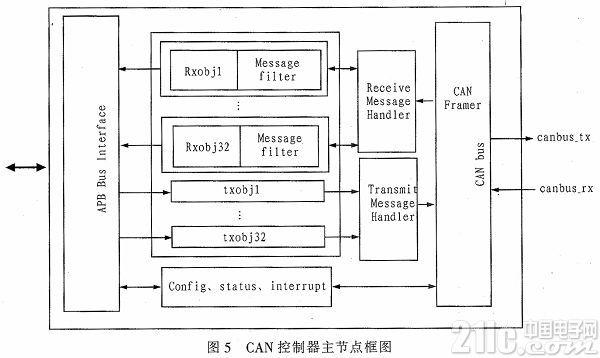

Cortex—M3內部集成的CAN控制器對如圖5所示,控制器從CAN總線上接收和發送串行數據,并將數據傳遞給報文處理器。報文處理器基于當前的過濾設置以及報文對象存儲器中的標識符,將合適的報文內容載入與之對應的報文對象。報文處理器還負責根據CAN總線的事件產生中斷;報文對象存儲器是一組32 個完全相同的存儲模塊,可為每個報文對象保存其當前的配置、狀態以及實際數據。用戶可直接配置報文對象存儲器完成數據的發送和接收配置。

CAN總線節點的軟件設計主要包括CAN節點初始化、報文發送和報文接收。使用控制器之前,需設置CAN的工作時鐘(40 MHz)并配置用于傳輸CAN信息的GPIO管腳。

2)冗余程序設計

系統使用了兩條完全獨立的CAN總線數據通道,實現了物理層、數據鏈路層的全面冗余。獨立的控制器能夠檢測到自己通道的故障,但CAN協議規范定義的數據鏈路層和部分物理層并不完整,需要通過軟件冗余模塊來實現總線狀態的監控、網絡故障的診斷和標識處理。

在熱冗余的情況下,本地節點主控制器同時打開兩個總線控制器的中斷。當網絡其他節點發送數據幀/請求幀時,如集一個CAN控制器到它相對應的總線上的任一環節發生故

障,則相應的總線控制器不會產生中斷,控制器收到的數據則是另一個沒有產生故障的總線上的數據。如果本地兩個總線控制器同時接收到同一個報文,并分別向主控制器Cort ex—M3申請中斷。當有一個總線控制器申請成功時,則在中斷服務程序中關閉中斷,進行數據處理。如果接收到的報文有效,主控制器則對數據進行處理,處理完畢后,加入低延時、清除所有的中斷并在退出前打開所有的中斷。另一個CAN總線控制器的中斷,如果是同時到達的則被清除,如果是稍后到達的,則會因為中斷處理程序的延時也同樣會被清除。如果接收到的報文無效,主控制器將清除本次控制器申請的中斷,退出中斷處理函數。此時,另一個CAN總線控制器的中斷會被響應,主控制器會判斷接收到的報文是否有

效,并采取相應措施。

4 結束語

本文的設計創新點在于提出了基于SoC技術與IP核復用技術的星載計算機CAN網絡模塊冗余設計,與傳統的星載計算機外擴兩片CAN控制器的冗余設計方案相比,本設計充分利用SoC技術實現內置兩路CAN控制器,簡化電路設計、節省了星載計算機單板體積且采用公開開放免費的軟IP以及自行開發的軟IP核達到降低成本的目的降低了成本。

評論