基于DSP的1553B總線接口電路設計

機載火控數據采集技術需要滿足實時采集、實時傳輸、實時存儲以及方便下載的需求,以便于地面人員對獲取信息的處理。這樣可以更好的動態掌握飛機的作戰狀態,提高飛行訓練效果和作戰能力。1553B數據總線作為航空電子綜合系統中信息交流的主干道,使機載數據能在復雜的環境中得以保存、交換。DSP作為高速性能的數據處理芯片,可以實現較高速率的數據采集。FPGA作為高速、復雜的組合邏輯和時序邏輯控制器件,更適合外圍電路的連接,將兩者組合使用,滿足了數據的高速傳輸與存儲。同時,隨著1553B數據總線協議標準的頒布,許多電器件公司開發了能將1553B數據總線與CPU相連接的相應接口芯片。這樣,使得數據在傳輸過程中更加穩定、高速、可靠。本文旨在探討采用DSP與相應接口芯片BU-61864,設計相關電路來實現機載火控數據的采集。

本文引用地址:http://www.j9360.com/article/201609/304031.htm1 1553B數據總線

MIL_STD_1553B是軍工定義的數字時分制命令/響應式多路傳輸數據總線,采用曼徹斯特Ⅱ編碼,半雙工工作方式,數據傳輸的速率為1Mbps,能掛接31個遠置終端,支持3種終端類型。該標準作為美國國防部武器系統集成和標準化管理的基礎之一,被廣泛應用于飛機綜合航電系統、外掛物管理與集成系統,并逐步擴展到飛行控制等系統及坦克、艦船、航天等領域。我國參照MIL_STD_1553B標準,于1987年頒布了相應的軍用標準,即GJB-289A。

MIL_STD_1553B定義了連接在總線上的3種類型終端,即總線控制器(BC)、遠程終端(RT)和總線監視器(BM)。

1)總線控制器(Bus Controller簡稱BC):總線控制器的功能就是控制總線上的數據流收發,數據總線上有很多BC,但是每次只能一個BC工作。而且一些RT也能擔任BC的工作。BC發送命令給RT,接收并確認命令之后,RT給出響應。

2)遠程終端(Remote Terminal簡稱RT):RT是一個采用1553B數據總線連接各式各樣子系統的設備,RT接收BC傳送的命令、檢測錯誤并且反饋錯誤,即要對BC作出響應。

RT特征如下:

①一條數據總線可以連接多達31個RT。

②每一個RT可以有多達31個子RT。

③RT只有當接收并確認BC的命令之后,才會作出響應,屬于被動式。

3)總線監控(Bus Monitor簡稱BM):BM監聽總線上的所有數據傳輸并且記錄指定的消息。他們的連接如圖1所示。

1553總線上的數據是以串行數字脈沖編碼調制的格式進行傳輸,采用的是曼徹斯特Ⅱ雙相電平碼作為數據的編碼格式。邏輯1電平由I/O編碼組成(即一個正脈沖后面緊跟著一個負脈沖),邏輯0由0/1編碼組成(即一個負脈沖后面緊跟著一個正脈沖)。

1553B總線上的信息是以字的形式傳輸的。包括一個3位的同步位、16位信息位以及一位奇偶校驗位。總線上的字共有3種類型:命令字、數據字、狀態字。他們的具體格式如圖2所示。

2 硬件選擇

2.1 TMS320C6713芯片介紹

DSP芯片選用TI公司生產的TMS320C6713,該芯片為TMS320C6000系列DSP平臺上產生的新的浮點型芯片。其有225 MHz的高速運行速度,提供13.5億次/秒浮點運算,18億/秒的指令操作。而且,C6713使用2級緩存的架構以及強大多樣化的外設集:1級程序緩存是一個4 kB的直接映射高速緩存,1級數據高速緩存是一個4 kB的2路組相聯高速緩存。2級內存和緩存有一個256 kB的存儲空間,在程序和數據之間共享。這個256 kB存儲器中64 kB可以配置為寄存器、高速緩存或者兩個的組合,192 kB作為對應的SRAM。可見,C6713應用非常靈活。外設集包括2個多通道緩沖串行端口(McBSPs),2個內部集成電路(I2C)總線,一個專用通用輸出/輸出(GPIO)模塊。2個通用定時器,主機接口(HPI),以及1個能夠與SDRAM、SBSRAM、異步外設無縫連接的外部存儲器接口(EMIF),增強型直接內存訪問(EDMA)控制器(16個獨立通道)。

C6713有著非常好的運算能力、高效的指令集、智能外設、大容量的片內存儲器和大范圍的尋址能力。因此,更適合用于對運算能力和存儲量有較高要求的場合。

2.2 BU-61864芯片介紹

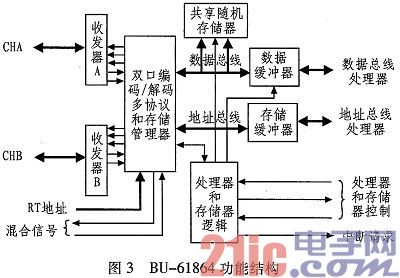

由于本文選用的DSP芯片C6713的I/O電平為3.3 V,為簡化硬件電路設計,選用DDC公司的全3.3 V的1553B協議芯片BU-61864,這樣無需電平轉換,大大提高設計效率和減少相關工作器件。BU-61864芯片內部集成了雙收發器、編/解碼器、協議邏輯、內存管理和中斷控制邏輯,支持BC/RT/MT模式,還提供了一個4kB的內部共享靜態RAM和與處理器總線之間的緩沖接口,并且有可擴展的4K*17bitRAM,兩個1553B收發器芯片。

BU-61864有靈活的接收/存儲器接口,能完全實現1553B協議所規定的消息傳輸外,還具有較強的消息管理能力,能全面兼容1553B協議。其功能結構框圖如圖3所示。

3 硬件接口電路設計

本系統由DSP主導,1553B協議部分由BU-61864協議芯片完成,外接邏輯電路由FPGA器件完成。其中DSP控制BU-61864的初始化以及消息的讀取和處理。FPGA實現信號的控制和譯碼。而在DSP對BU-61864相關寄存器的控制和配置后,它可以工作在BC、RT或BM等模式下。在本次操作中,因為只需要記錄來自機載火控系統的所有數據,因此只工作在總線監視器模式下即可。

當BU-61864接收到一個消息后,產生一個中斷信號,該中斷信號就會向C6713發送一次中斷申請,C6713響應中斷,并向相關寄存器做出配置。在BU-61864和C6713之間的控制邏輯電路由可編程邏輯芯片FPGA實現。控制邏輯電路包括地址譯碼電路和邏輯控制電路。其中地址譯碼電路功能是對接口芯片所使用的C6713存儲器和BU-61864存儲器進行地址選擇和譯碼;而邏輯控制電路功能是產生BU-61864所需要的控制信號以及提供給C6713中斷信號、握手信號、插入等待信號。所有的數據總線和地址總線,以及控制信號、中斷信號都是由C6713和BU-61864提供給控制邏輯電路。它們的具體電路連接如圖4所示。

評論