芯片設計中的功耗估計與優化技術

1 引言:功耗在芯片設計中的地位

本文引用地址:http://www.j9360.com/article/201609/303352.htm長期以來,設計者面臨的最大挑戰是時序收斂,而功耗處于一個次要的地位。近年來,下面的因素使功耗日益得到設計者的關注:

1)移動應用的興起,使功耗的重要性逐漸顯現。大的功耗意味著更短的電池壽命。

2)芯片集成度的提高,使供電系統設計成為挑戰。

隨著工藝的進步,芯片內的電路密度成倍提高,并且運行在以前數倍的頻率之上,而片上連線則越來越細,片上供電網絡必須將更多的電力以更少的連線資源送至每個單元,如果不能做到這一點,芯片的穩定性和預定工作頻率都將成為問題。IR壓降和供電網絡消耗的大量布線資源成為困擾后端設計者的重要問題,現在這種壓力正在一步步傳導到前端設計者的身上,要求在設計階段減少需要的電力。

3)功耗對成本的影響日益顯著

功耗決定了芯片的發熱量,封裝結構需要及時把芯片產生的熱量傳遞走,否則溫度上升,造成電路不能穩定工作。因此,發熱量大的芯片需要選擇散熱良好的封裝形式,或者額外的冷卻系統,如風扇等,這意味著成本的增加。

基于以上原因,功耗成為產品的重要指標與約束。下面的因素在設計之初,就應當列入設計者的考慮范圍:

1)功耗目標的確定

a) 產品的應用領域中功耗指標的商業價值;

b) 封裝,制程的成本影響;

c) 實現的可行度,復雜度,由此帶來的設計風險和時程影響的評估;

d) 參考值的選取:根據同類產品,經驗值,工具分析確定,并隨著設計的深入不斷修正。

2)優化方案(策略)的設定

在進一步分析之前,我們先看一下功耗的組成。

2 功耗的組成

2.1 core power

功耗的組成包含RAM、ROM、時鐘樹(clock tree)和核心邏輯電路(Core logic)等四部分,下面依次來分析。

1)RAM

RAM功耗的計算是項復雜的任務,幸運的是,memory compiler可以為我們進行此項工作。關鍵點在存取每個端口的速率,這可以通過考慮存取pattern類型得到,或者通過仿真得到。建議在設計初期即生成不同參數(寬度,深度,速度,port數)的RAM/ROM的功耗數據,以利于設計探索。

2)時鐘樹

時鐘樹的功耗占到整個芯片功耗的40%~60%,因為它的高活動率(100%)和正負邊沿均消耗電力。

其中,電容包含寄存器的電容,驅動單元的電容和連線電容三部分。

3)核心邏輯電路

定義核心邏輯電路功耗為除時鐘樹外的組合與時序單元消耗的電力。由兩部分組成:

leakage current

capacitive loads

4)宏單元(macro cell)

多數芯片包含PLL等模擬macro,可以從庫提供商的數據手冊找到其功耗參數。設計者可以通過切分系統模式關閉不需工作的模塊,以減小功耗。

2.2 IO power

IO功耗包含IO單元、外部負載、外部終端等。因為需要驅動板級的連線,IO的電容會是內部單元的數百倍量級,因此消耗較多的電力。有時候,IO的功耗可以占到整體功耗的很大比例,系統架構可能因之改變,如:重新定義系統的劃分,以減少芯片-芯片的連接;選擇不同的IO接口協議,以減少能量消耗。IO 功耗通常由系統架構,接口帶寬與協議要求決定。一旦庫選定,設計者可以優化的空間很小,但是核心的功耗是設計者可以減小的,在后面的篇幅中,我們將以核心功耗的估算與優化作為主題。

3 功耗估算

功耗估算的價值是盡可能早地以定量方式看到優化結果,以助于設計者的初期架構探索。在每個階段, 如產品規劃、架構制訂、代碼書寫、綜合、PR等,設計者都面臨若干選擇,能馬上看到選擇的結果,而不是到設計流程的末尾,可以有效減少開發時間。

3.1估算的方法

功耗的估算可以在設計流程的各個階段進行,對應設計表征的不同形式。

software level ->behavior level -> RT -> gate -> circuit

越早的階段,抽象層次越高,其精確度越差,但可以更早給設計者反饋,同時得到估算結果消耗的時間越少。

1. 軟件級

首先,定義系統將執行的典型程序。典型的程序通常會有上百萬的機器周期,進行一次完整的RTL級的仿真可能需要數月時間,這是不可接受的。解決的方法是在更高層次建立基本組成單元的功耗模型。

比較實用的方法是根據特定的硬件平臺,統計出每條指令對應的功耗數據,進行指令級的仿真。

2. 行為級

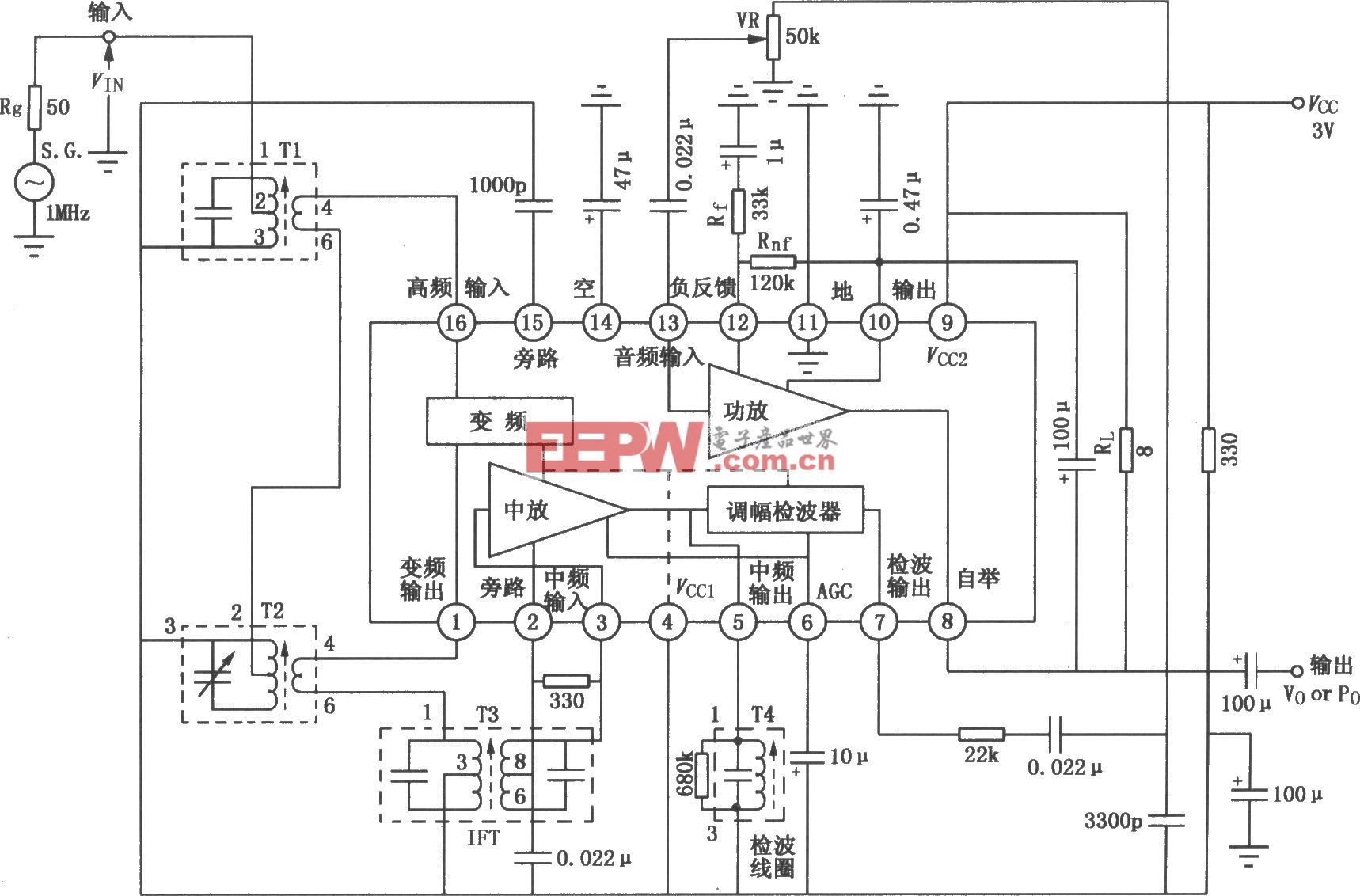

在進行分析前,我們首先應了解電路的功率消耗原理,實際電路的電力消耗如圖1所示。

圖1

Prms = 1/2 * f * Vdd^2 * sigma(Ci * Ai)

--- f : clock frequency

--- Vdd : voltage

--- Ci is capacitance load of node,

--- Ai is the average switching activity of their node

在行為級設計表征中,物理電路單元尚未建立,難點是得到電容與活動率的值。存在兩種思路:

1) 理論估計:

根據電路復雜度得到C,復雜度由算術,邏輯操作的數量,狀態的數目與轉換率衡量。

complex = f (arith ope, boolean ope, state, transition)

可以根據信息理論估算活動率。

2) 實驗估計:

由快速綜合得到寄存器傳輸級的原型,進而估計電容與活動率。

3. 寄存器傳輸級

第一步是在庫中為高層的設計組件建立功耗信息算式,得到方式是在不同環境變量組合下通過仿真,統計功耗數據,繪制成曲線形式。然后,通過靜態分析電路結構或動態仿真,收集電路動作幾率數據,代入上述算式,得到各個組件的功耗值。最后,把所有組件的功耗值求和,得到總功耗。

4. 門級

與寄存器傳輸級的區別在于,基本單元是工藝庫中的標準單元,功耗方程通過電路仿真得到,所以更精確。

5. 晶體管與版圖層

所有的連線的電容、單元的負載,驅動都已得到,根據晶體管和連線模型的電壓、電流方程,可以算出精確的功耗數據。

評論