利用模數轉換器的特性降低物聯網系統級芯片功耗

諸如物聯網(IoT)這樣的功耗敏感型應用要求在系統級芯片(SoC)內部有一套全面的低功耗策略。單純依賴傳統關閉電源模式和低電源電壓的技術可能不足以實現功耗目標。模擬模塊通常被認為是過于敏感,并且與激進的電源管理技術不兼容。

本文引用地址:http://www.j9360.com/article/201602/286622.htm然而,對于模擬模塊特性的全面了解可以使低功耗SoC設計成為可能。在本文中,我們對通用的物聯網SoC設計中與外部傳感器連接的模數轉換器(ADC)知識產權(IP)進行了近距離的觀察,并描述了其相關特性,以及在系統層面上如何利用這些特性來實現低功耗。

傳統低功耗技術的挑戰

那些有可能依靠紐扣電池或能量采集來供電的物聯網應用,正在驅動整個行業對超低功耗SoC設計的需求。為了在不替換電池的情況下,維持很長一段時間的運行,設計人員必須充分利用可用的低功耗技術。

傳統的方法依賴于SoC電源電壓的降低,以及更先進的半導體工藝提供的更小特征尺寸來降低運行功耗。這種方法增加了系統成本,且有可能導致更高的漏電。

在系統層面上,可以通過識別芯片中哪些模塊可以在操作完成后關斷電源,來實現低功耗技術;也可以將時鐘頻率和電源電壓調低至維持必要操作所需的最低值,從而降低額外的功耗。

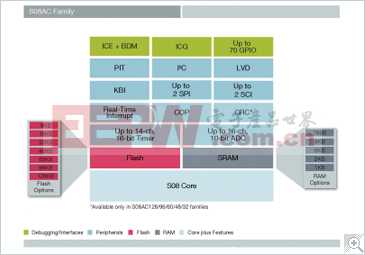

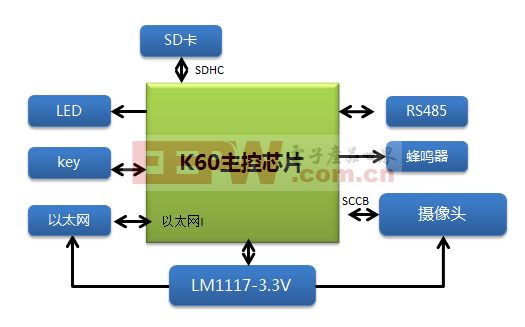

一款物聯網SoC的典型任務場景可以在其非常短的工作周期中標定出來:大部分電路通常都處于空閑模式;僅有一小部分電路始終處于工作模式,以便掃描環境以及在需要時激活其余的電路。圖1所示為常見的物聯網使用情況。始終處于工作模式的電路被放置在一個專用的電源島上,并使用高閾值(Vth)電壓器件甚至厚氧化層器件來使漏電最小化。其余的電路可以通過切斷其電源限制其漏電。

圖1常見的物聯網應用場景

一款語音控制的裝置就是這種應用的案例之一,其中只有簡單的語音監測電路始終處于工作模式;而專門用于指令識別和處理的模塊,則只有在語音監測電路識別出一個可能的命令時才會被激活。另一個案例就是傳感器的定期輪詢,它是用來決定是否需要根據環境中的一些變化而采取進一步的行動。

因此,為了進一步降低工作和漏電功耗,現代的物聯網SoC設計引入了復雜的電源管理架構,其帶有多種電源關斷模式,并將電路詳細地分割到不同的電源島中。

支持當今物聯網SoC設計的全新低功耗技術

然而,當提到模擬接口時,傳統的低功耗技術就不能直接應用了。模擬模塊通常要去處理具有大電壓擺幅和高線性度要求的信號。這就限制了降低電源電壓的可能,也因此限制了縮小實際最小特征尺寸的能力。

模擬模塊存在內部偏置電流和偏置電壓,為了實現最佳性能,它們需要得到妥善的處置。因此,上電和關斷時間自然就慢,從而限制了電源模式切換的使用。此外,它們有時是通過較慢的串行總線控制的,這就導致了對其電源狀態進行實時、主動控制的能力受到限制。

設計人員需要一種新的方法來突破這些局限性,尤其是在設計功耗敏感型應用的時候。集成與傳感器連接的模數轉換器(ADC)不僅降低了外部物料清單(BoM)成本,而且也支持了在SoC的電源管理架構中實現更緊密的模擬接口集成,實現了更快的上電和關斷轉換以及額外的功耗降低。為了降低BoM成本和功耗,設計人員必須選擇一款可集成的ADC,它需要足夠靈活地支持不同的操作模式,并且可以在不同的電源模式間快速轉換而功耗最低。一款可集成的ADC具有以下關鍵特性:

l 最低的靜態功耗,在速度降低時可實現功耗最小化

l 多種性能模式,在性能設置降低時可實現功耗最小化

l 具有多種電源模式,以及在它們之間快速轉換且不會損失精確度和性能

具體的使用案例

設計人員必須理解ADC的所有特性,以及如何在具體的使用案例中應用來實現額外的功耗降低。以下是幾個使用案例的實例。

1. 非常緩慢的采集速度

本案例考慮的是這樣一種情況:系統數據處理需要某一種時鐘速度以實現所需的處理吞吐量,然而傳感器信息可能只需要以一種很低的速率來更新。

對于這個使用案例,傳統的實現方法是對處理器時鐘進行分頻降低來匹配傳感器采樣所需的低速率。然而,這個時鐘頻率可能比ADC能夠可靠支持的最小值還低——還有一種選擇就是以更高的頻率來設定ADC時鐘,但在某些時段需要保持空閑(待機)模式。

理想的選擇是在這些空閑期內完全關閉ADC,然后在下一次傳感器采樣時快速喚醒它。在這種模式中,ADC主要消耗漏電功率,而僅在短暫的主動采樣時刻消耗工作功率。這有效地將功耗的低限擴展到了比時鐘頻率最小值時的功耗值低得多的范圍,而且不影響SoC的配置(例如,符合數據處理所需的時鐘速度)。

這種選擇依賴于以下ADC特性:

l 快速的關斷和上電步驟(諸如校準等任何緩慢的過程都應該避免出現在這些步驟中)。

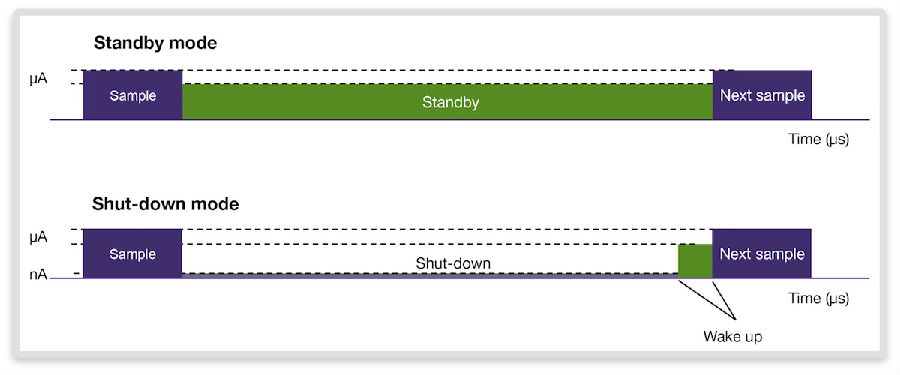

l 關斷模式下非常低的漏電功耗,例如將電源管理功能集成到ADC中(電源開關、低壓差線性穩壓器等)。在不同電源模式之間轉換所造成的額外功率損耗應該是最低的(圖2)。

圖2待機模式和關閉模式中的低功耗對比

l 性能的可重復性。像偏移和絕對精度這樣的性能參數需要在連續多個電源周期中都保持一致。轉換結果的穩定性可以使用“有效分辨率”(Reff)這一度量標準來判定,該標準可以從ADC依據一個固定輸入而產生的輸出直方圖中獲得,而該直方圖則由多個電源周期中的大量測量值樣本來形成(圖3)。比較窄的分布(圖3左側)是更好穩定性(及低噪聲)的證明。而擴展的分布或重復出現多個峰值(圖3右側)則是穩定性較差的象征。

圖3 ADC的有效分辨率直方圖

2. 與內部處理器和電源管理系統緊密結合

本例考慮了這樣一種情況:集成的ADC與處理器寄存器緊密結合,使ADC控制寄存器映射至處理器的內部寄存器中,從而避免了通過復雜的總線去控制ADC,而這些總線通常每次讀/寫操作要好幾個時鐘周期。這種技術可支持系統快速地進入低功耗模式,不用多個時鐘周期來控制ADC。如果ADC常常經歷上電/斷電周期,那么該技術將是大有裨益的。

此外,穿越模擬域和數字域的控制回路的延遲變小了,從而潛在地提升了控制回路性能。

這種技術依賴于以下ADC特性:

l 將ADC控制映射到內部處理器寄存器中,或直接映射到AMBA結構中(AMBA即高級微控制器總線架構)的能力,避免了循環和電源等待周期。

l 將ADC電源管理特性(內部電源島等)集成至SoC電源管理系統中的能力

3. 性能分級

本例考慮了這樣一種情況:某個傳感器的讀數所需精度可以根據系統狀態而變化。例如,當一個圖像傳感器檢測到沒有任何活動時,較低的精度是可以接受的。然而,當有活動被監測到時,可能就需要更高的精度。

這項知識可以被用來降低功率損耗:數據采集速度和ADC性能等級在非活動期間可以降低,而僅在需要更高精度時才升高。

這種技術依賴于以下ADC特性:

l 帶有相應功耗降低措施的不同精度選項

l 動態的采樣率控制,以及功耗和采樣率成比例降低

4. 高輸出阻抗傳感器

本例考慮了這樣一種案例:使用開關電容技術來實現現代的ADC。為了實現一種簡化的電路分析,這些ADC的前端采樣級可以被簡化為一個電容器(采樣單元)和一個非線性電阻(開關)。傳感器本身可以被簡化為一個電壓源和一個串聯電阻(輸出阻抗)(圖4)。

圖4簡化的ADC輸入電路和傳感器原理圖

當電路閉合時,傳感器就充當一個加載采樣電容的源,時間常數τ=RC。如果傳感器輸出阻抗很大,那么時間常數也大,可能就沒有足夠的時間來建立采樣電容的電壓到一定精度。

避免這種限制的一種方式是在傳感器和ADC之間插入一個低輸出阻抗的緩沖器。然而,這種解決方案會因為緩沖器本身消耗的電能而導致大量額外功耗。

一種理想的解決方案是延長ADC的采樣時間以適應所需的建立時間。如此一來,就不需要緩沖器了,同時功耗也降低了。(圖5)。

這種技術依賴于以下ADC特性:

l 可編程的采樣時間,它可以根據傳感器決定的設置要求而調整,既可以為高阻抗傳感器而延長(避免額外的緩沖器),也可以為低阻抗傳感器縮短(使ADC能更早進入關斷模式,或開始一個新的轉換周期)。

圖5延長采樣時間以適應高阻抗傳感器

總結

了解模擬接口的特性和使用案例,可以幫助設計人員大幅度地降低物聯網SoC設計的功耗。

通過集成與傳感器連接的ADC,可以實現功耗降低。集成的ADC有如下特性:最低的靜態功耗,即隨速度的降低而實現功耗最小化;多種性能模式,其中隨著性能設置的降低而實現功耗最小化;多種功耗模式,以及在它們之間的快速轉換、且不會損失精確度和性能的能力。

設計人員必須重視這些特意提供的使用案例,并利用集成ADC的先進低功耗技術和其它特性,來實現額外的功耗降低,同時滿足性能要求。

作者:Synopsys技術營銷經理Manuel Mota

評論