Zeno開發特殊SRAM 可提升MOS結構效能

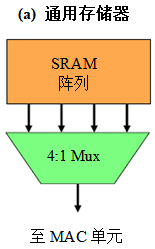

Zeno Semiconductor日前開發出將最小靜態隨機存取存儲器(SRAM)納入單一MOS電晶體技術,不僅其采用記憶單元(bit-cell)數量變多,存取時間也可大幅縮短4成。

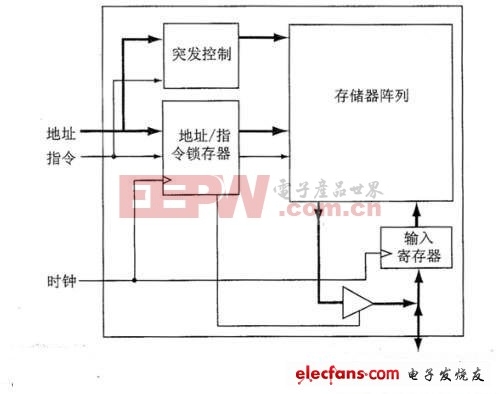

本文引用地址:http://www.j9360.com/article/201601/285239.htm據EE Times網站報導,Zeno在國際電子零組件會議(International Electron Devices Meeting)上展示這項新技術。Zeno執行董事長Zvi Or-Bach表示,該技術之所以讓N型MOS電晶體做為穩定SRAM,主要是透過采用2個本質雙極N-P-N型電晶體所賜。

該技術看似為3個電晶體記憶單元,但由于是采用本質元件,具備開放閘極與共集電極的雙極N-P-N型電晶體可被視為虛擬電晶體。換句話說,并未占據多余芯片空間,為一善用單一MOS電晶體架構的范例。

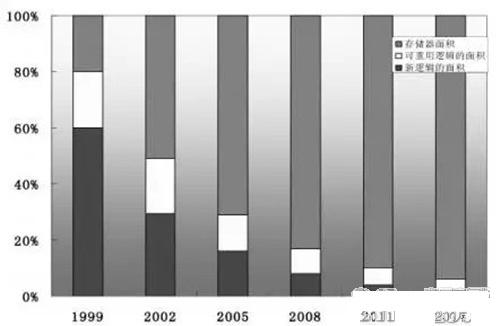

另外,其記憶單元大小也只有0.025平方微米,比一般0.127微米還小。

Zeno 28奈米SRAM記憶單元大小也比三星電子(Samsung Electronics)10奈米FinFET SRAM記憶單元小37%,不管采用3D FinFET或全空乏絕緣上覆矽(FD-SOI)平面晶圓,即使在先進制程仍可維持其大小水準。

Zeno也希望透過2款電晶體滿足利基市場需求,包括擁有5倍記憶單元的單一電晶體以及增加1個存取電晶體成為雙電晶體記憶單元,來降低漏電流與存取時間達4成的電晶體,同時其記憶單元仍多出3倍。

該公司執行長Yuniarto Widjaja指出,單電晶體Bi-SRAM主要鎖定對價格敏感及強調低功耗的市場,例如物聯網(IoT),后者雙電晶體則瞄準網路或高效能運算(HPC)等市場。其大小技術優勢可在FinFET或FD-SOI等先進制程或較早制程上得以發揮,Zeno也針對邏輯與存儲器芯片推出架構。

評論指出,一旦Zeno透過雙功能數位電晶體將其他元件縮小尺寸,將等于可避免繼續透過采取更先進制程微縮必要性。有別于一般公司采取持續微縮芯片做法以便容納更多電晶體,Zeno則是開發更少與更小電晶體技術來達到同樣效果。

Zeno技術優勢并非只有采用本質雙極電晶體,同時也省略會占用芯片面積的電容器等元件。換句話說,雖采用標準CMOS制程,但可達到元件小5倍以及存取時間更快40%的結果。

Zeno架構與制程目前擁有50件以上專利,該公司則透過授權IP方式向其他公司開放,不過并未透露其客戶名單。

評論