高精度數字信號中和器的設計與實現

0 引 言

高精度的時間測量在高能粒子物理研究、深空通訊、激光測距和物質成分檢測等領域均有著廣泛的應用。而時間測量儀器快速、高精度、高靈敏度的特點決定其必須具有高時間分辨率和高靈敏度的數據采集及處理設備,目前最常用的有數字信號中和器(Digital Signal Averager)和高精度的時間數字轉換器(Time-to-digital converter,TDC)。其中TDC的原理是通過記錄一段時間內離子脈沖信號相對于觸發信號(start)的到達時間和數量,繼而判定粒子的種類及其含量。

但是TDC的原理決定了其固有的缺陷-“測量死區”,即當有多個粒子同時到達時,前端儀器(如飛行時間質譜儀)產生脈沖的幅度是與粒子的數量成正比的,但是TDC的原理決定了其只認為此時到達了一個粒子,從而丟失了幅度信息。故利用TDC進行定量分析時,就存在了“測量死區”。而利用超高速數字信號中和器進行測量時,由于可以同時采集到脈沖的幅度和時間信息,故可以進行高速、高時間分辨率的定量分析。

本文主要介紹了一種高精度數字信號中和器的設計與實現方法,其最小時間分辨率為333ps,測量時間范圍為0~20μs,系統死時間50ns,并已在飛行時間質譜儀器中得到應用。

1 總體結構與基本工作原理

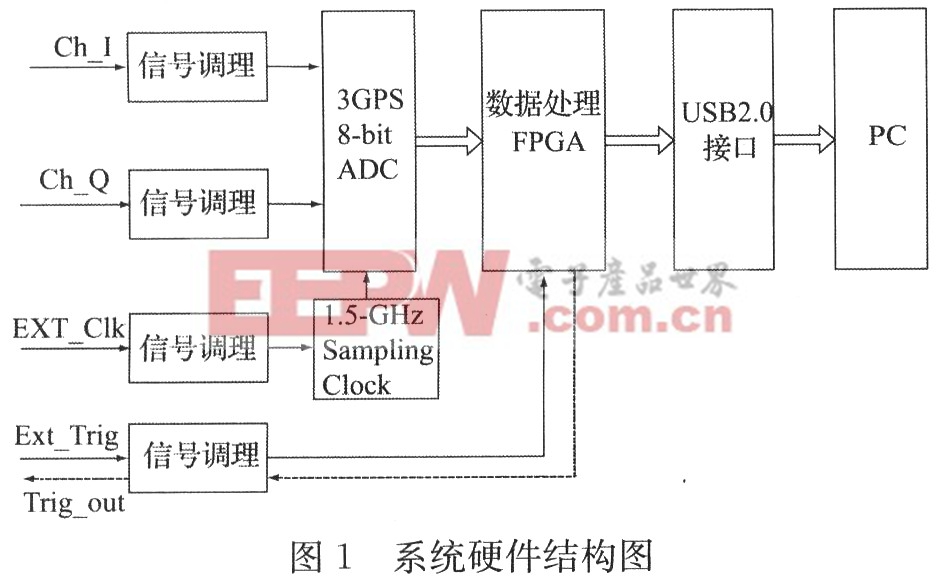

圖1所示為本系統整體硬件框圖,數字信號中和器主要由前端信號調理模塊、射頻采集模塊、高速時鐘產生模塊、FPGA模塊、USB接口模塊等部分組成。其中信號調理模塊主要由前置放大器ERA_1+和變壓器ADTL2_18組成。射頻采集模塊主要由ADC08D1500及相關外圍電路組成。高速時鐘產生模塊由ADI公司的時鐘產生芯片AD9517-4組成。數據處理及控制模塊由XILINX VIR-TEX-4 SX35 FPGA及相關外圍電路組成。USB2.0傳輸及控制模塊由Cypress公司的CY7C68013及相關外圍電路組成。

本數字信號中和器具有內、外觸發兩種工作模式。在內觸發工作模式下,由系統自身產生觸發(start)信號,并由觸發通道輸出電子引導脈沖信號,以引導質譜儀前端設備。而在外觸發工作模式下,系統采集外觸發信號的到達以作為轉換的開始。

當射頻采集模塊工作在單邊沿采樣時,通道I和通道Q為獨立的stop信號采集通道,最高采樣率為1.5GSPS;當射頻采集模塊工作在雙邊沿采樣時,通道I和通道Q只能有一個作為信號采集通道,最高采樣率為3GSPS。以外觸發、雙邊沿采樣工作模式為例。觸發通道采集外部觸發信號以作為轉換的時間起點,脈沖輸入信號經前置放大、電平轉換等信號調理后,進入射頻采集模塊。在雙邊沿工作模式下,高速時鐘產生電路提供1.5GHz的采樣時鐘,從而可以使射頻采集模塊的最高采樣率為3GSPS。ADC采樣的結果分DI、DQ、DID、DQD4組8bit差分信號以DDR的形式傳至FPGA,每組差分信號的速度為375MHz。FPGA啟動相應邏輯,以50us為一周期,連續采集1s,每周期內持續采樣時間20us。同時FPGA邏輯控制將不同周期內相同時刻的采樣點對應相加,從而得到1s內累加的質譜圖。最后FPGA通過USB控制邏輯將包含脈沖數量和到達時間信息的質譜圖通過USB2.0接口傳至PC以完成質譜圖的繪制和后端信號處理。由于射頻采集ADC的最高采樣速率為3GSPS,即可達到333ps的時間分辨率。針對不同的應用背景,射頻采集模塊的時鐘頻率可調,調節范圍為500MHz~3GHz,即時間分辨率為333ps~2ns可調。

2 系統重要模塊設計與實現

2.1 前端信號調理模塊

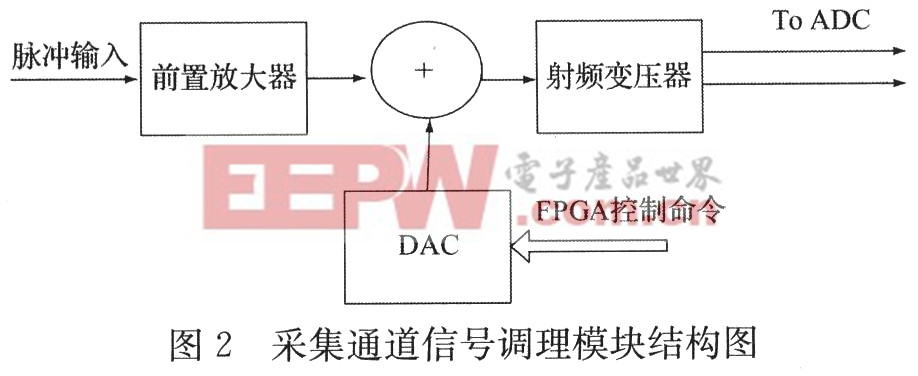

在氣體行業檢測的應用中,飛行時間質譜儀器中離子探測器的輸出信號一般為NIM信號,幅值在0~-100mv,而超過此范圍的大信號通常為H2O+及OH+等飽和信號,對測量結果影響不大,故不予考慮。由于輸入信號幅度較小,為提高測量測量精度并充分利用ADC的量化范圍(650mV),設計中在采集通道的信號調理模塊利用微波管Mini ERA_1+完成前置放大。ERA_1+的3dB帶寬為DC~8GHz,內部與50歐傳輸線匹配,最大增益12dB。同時,由于ADC08D1500要求差分輸入,故信號調理模塊在前置放大后利用射頻變壓器Mini ADTL2_18完成單端信號到差分信號的轉換。圖2所示為采集通道信號調理模塊結構圖。

評論