多路測量信號擴頻傳輸的DSP系統實現

路測量信號擴頻傳輸,結合了擴頻通信和 DSP的優點 [3-4],是一種有發展前途的檢測信號傳輸實現方式。

2. 多路檢測信號的擴頻傳輸系統系統的組成按照功能劃分為發射模塊和接收模塊。在發射模塊中,多路基帶數字信號(模擬信號則先通過模數轉換)分別由各自對應的偽隨機序列進行擴頻調制,這些偽隨機序列各不相同但相互正交(或準正交),用這些序列進行擴頻調制同時利用碼分復用技術把多路信號復合成一路信號送主調制器進行載波調制后,再發射出去。 在接收模塊中,先對接收到的信號進行載波解調,然后再用本地的與每一路已同步好的偽隨機序列進行相關解擴,因為各路信號對應的偽隨機序列互不相關,因而可恢復出每一路原始的基帶信號,這里的信號是指數字信號,若需要模擬信號,則可把數字信號轉換成模擬信號。本系統對接收模塊的偽隨機序列的同步采用常用的滑動相關捕獲來實現[5]。多路測量

信號擴頻傳輸系統的組成原理圖如圖 1所示。擴頻傳輸系統中,擴頻信號帶寬 B 2與信息帶寬 B 1之比稱為處理增益GP,即

在擴頻通信中,接收機作擴頻解調后,只提取擴頻序列相關處理后的帶寬 B 1的信號成分,而排除掉擴展到寬頻帶 B 2中的外部干擾、噪聲和其它用戶通信的影響,所以擴頻處理增益 GP能夠準確反映擴頻通信的抗干擾的能力。

擴頻序列的碼長N越大,碼元寬度 TC越小,則碼速 Rc越大,擴頻通信系統的擴頻增益也越大。

擴頻處理增益越高,系統的抗干擾能力越強。以周期為 127的 Gold序列為擴頻序列的一路信號的傳輸過程為例,數據的發送頻率為 19200,擴頻序列的頻率為 19200×127,誤碼率是未擴頻傳輸的 0.04417,數據接收時的誤碼率降低近兩個數量級。

本系統采用的 Gold擴頻序列的周期為127,其碼分多址的可以實現 12路的檢測信號的同時同頻的擴頻傳輸。多路檢測信號的擴頻傳輸可以保證在接收端的低誤碼率要求下實現可靠傳輸。

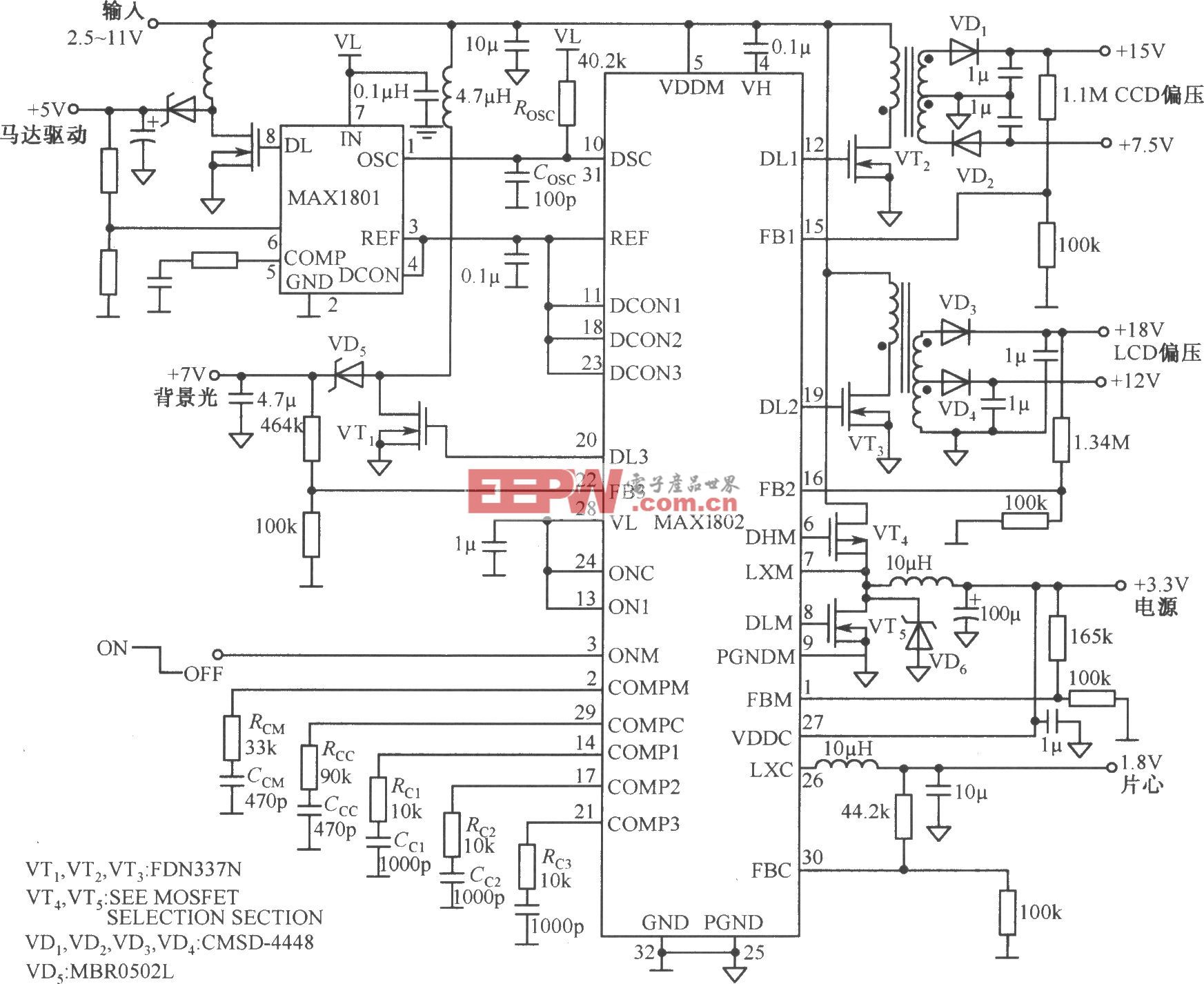

3. 多路檢測信號擴頻傳輸 DSP實現的系統結構多路測量信號擴頻傳輸系統主要實現多路測量信號(包括模擬信號和數字信號,模擬信號可先經 A/D轉換成數字信號,數字信號存儲在系統的存儲器中,然后再進行擴頻傳輸)的擴頻調制、同步、擴頻解調等功能,同時便于以后對其擴展以完成其他功能。由于這是一個 DSP硬件平臺的設計,所以保證了以后功能擴展的實現中盡量不改變硬件的設計或者對硬件設計改變很小,且只需要添加部分軟件或者對軟件進行修改就可以達到其功能擴展升級,所以盡量減少專用芯片的使用而采用具有擴展性的芯片。整個系統的總體設計框圖如圖 2所示。

在總體設計中,采用定點 DSP實現多路測量信號的擴頻調制、解擴,用 FPGA來實現擴頻信號的同步[7]。整個系統平臺包括數字信號處理器 (DSP)內核、 FPGA、存儲器、 A/D轉換、

JTAG接口等。根據現有的實際情況,數字信號處理器 (DSP)采用 TI(德州儀器)公司的 TMS320C5416[6],FPGA芯片選用 ALTERA公司的 EP1K100QC208-3,FLSAH存儲器使用 AMD公司的 AM29LV200,A/D轉換使用 TI公司的開關電容結構的逐次比較型 8位 A/D轉換器 TLC540。JTAG為仿真接口連接。

評論