基于PCIe總線的超高速信號采集卡的設計

摘要:設計一種基于PCIe總線的不間斷采樣和傳輸的超高速數據采集卡。利用雙400MHz、14位AID轉換器實現了800 MHz、14位的信號高速、高精度采集,論述了利用Xilinx公司FPGA的IPCORE設計實現PCIe總線控制接口。基于PCIe總線,采用乒乓交換數據傳輸的機制,實現了高速采樣數據流的不間斷傳輸。最后給出了實際采集數據的頻譜。利用該采集卡構成的數據采集系統在雷達偵察和干擾領域擁有很高的實用價值和廣闊的應用前景。

關鍵詞:數據采集;PCIe;FPGA;雷達對抗

在雷達對抗系統中,需要對于雷達信號進行實時測頻,并可以對感興趣的信號進行儲頻,為假目標欺騙干擾或壓制干擾提供測頻結果和儲頻數據。而數字測頻是當今發展最快的測頻技術之一。數字測頻、儲頻的關鍵技術之一即是超高速、高精度、不間斷的信號采集技術。采樣速率和精度的不斷提高,使得數據傳輸和存儲越來越成為數據采集系統的技術瓶頸。目前大部分高性能數據采集卡都是基于PCI、CPCI、VME等總線,最高持續傳輸速率難以超過400 MB/s,因此大多數采集卡采用采集和存儲分時工作的模式,即在板內設有一定容量的存儲器,當存儲器存儲數據到一定量時,停止采集而開始上傳數據,上傳完畢后再重新啟動采集,不斷循環,文獻也提出采集傳輸的流水工作模式,提高采集的效率。這些工作方式雖然也能滿足大部分數據采集的要求,但是在信號非常密集的環境中,交替工作模式將導致偵察截獲概率降低,帶來干擾的效能下降。基于上述原因,本文論述了一種基于PCIe總線的數據采集卡,該采集卡不但可以達到800 MHz/s采樣率、14 bit采樣精度,還具有不間斷采集、實時上傳的能力(在測頻只取其中8位分辨力,儲頻時取14位分辨力,根據系統的總數據量可編程)。該采集卡可以與高速信號處理器配合使用,構成信道化的數字測頻、儲頻系統,雙信道系統的組成示意圖見圖l。

1 系統總體設計

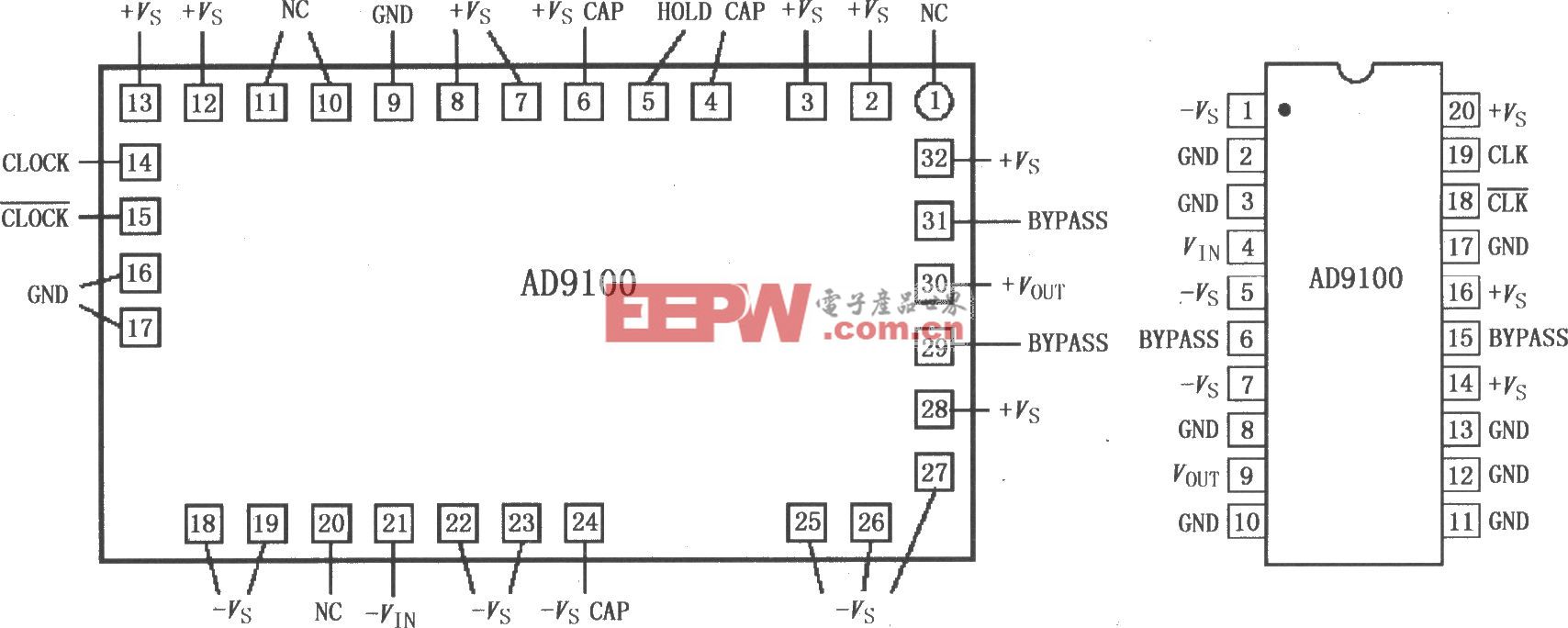

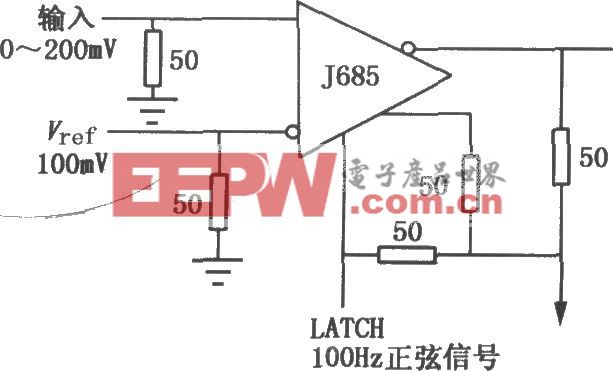

本采集卡的設計主要包括超高速A/D轉換器模塊、時鐘產生模塊、大容量存儲器模塊和基于FPGA的控制模塊。如圖2所示,待采集的模擬信號經過信號調理放大到合適的電平范圍,送入到兩片工作于交叉采樣模式的A/D轉換器,轉化后數字信號直接送至FPGA控制器,在FPGA內部實現信號電平轉換數據緩沖后,首先存儲于A路動態存儲器中,當A路存儲器存滿后,數據立即轉存于B路存儲器,同時啟動數據上傳操作,將A路存儲器的數據通過DMA方式上傳至主機存儲或傳輸到信號處理板中;當B路存儲器存滿后,數據存儲立即切換至A路存儲器,同時也啟動B路存儲器的上傳操作,如此反復循環。由于PCIe接口傳輸速率大于信號采集速率,因此可以保證數據的不丟失。

評論