基于邊界掃描的電路板快速測試系統設計

2.3 邊界掃描適配器設計

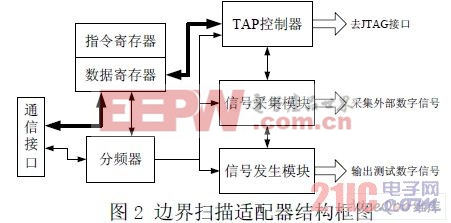

邊界掃描適配器采用Altera 公司的EPM7128SLC84-15 芯片作為控制器,負責與計算機 相連,上傳、下載測試數據和控制字,按時鐘產生邊界掃描控制時序及測試向量。芯片內部 按功能分應包含通信接口、指令寄存器、數據寄存器、TAP 控制器、信號采集模塊、信號發 生模塊和分頻模塊。結構框圖如圖2 所示。

從計算機傳來的指令信號和數據信號通過通信接口分別保存在邊界掃描適配器內部的 寄存器中,然后適配器中的其它模塊如TAP 控制器、信號采集模塊和信號發生模塊將依據 指令寄存器中的指令字進行相應的工作,包括發送JTAG 總線時序、移位、并行采集數據和 并行發送數據等。采集的數據通過通信接口上傳給計算機以供分析時使用。分頻器用來產生 各模塊工作所需要的時鐘信號。本文在MAX+Plus II 環境下,使用VHDL 語言對各模塊進 行設計,頂層文件使用圖形輸入方式將各模塊連接起來。

2.4 計算機軟件設計

本系統的計算機軟件采用Visual Basic 6.0 高級編程語言開發,其主要功能是通過計 算機并行端口實現計算機與邊界掃描適配器之間的實時通信,將指令信號和測試數據發送給 邊界掃描適配器,同時將測試響應數據上傳至計算機,并完成對數據的處理、顯示、存儲等 操作。

評論