基于TLV1578和TMS320VC5402的數據采集系統設計

摘要:在工業控制中,為了對數據進行實時處理,要求數據采集系統具有較高的速度和精度。在此設計了基于TMS320VC5402的快速數據采集系統,并詳細介紹一種A/D接口設計方案。通過對目標信號進行采集,結果表明該系統具有易實現,高精度,高穩定性等特點。提供了系統設計的結構框圖及實用的A/D接口原理圖,敘述了系統軟件的設計與實現過程,包括TLV1578的初始化和中斷服務子程序等。最后從工程實踐的角度給出了印刷電路板設計中需要注意的問題和相應的解決方案。

關鍵詞:數據采集;TMS320VC5402;TLV1578;A/D

0 引言

在工業控制中,經常需要將各種數據采集到計算機進行實時處理,這就要求數據采集系統速度快,精度高,并且具有數字信號處理能力。在此討論了一種基于TMS320VC5402的快速數據采集系統,并詳細介紹了該系統的A/D接口設計及軟件實現。

1 系統硬件設計

1.1 系統整體結構設計

該設計的數據采集系統的CPU為TMS320VC5402。該芯片是TI公司生產的從屬于TMS320C54x系列的一個工作靈活、高速、具有較高性價比、低功耗的16位定點通用DSP芯片。其主要特點包括:采用改進哈佛結構,1條程序總線(PB),3條數據總線(CB,DB,EB)和4條地址總線(PAB,CAB,DAB,EAB),帶有專用硬件邏輯CPU,片內存儲器,片內外圍專用的指令集,專用的匯編語言工具等。TMS320VC5402含4 KB的片內ROM和16 KB的雙存取RAM,1個HPI(Host Port Interface)接口,2個多通道緩沖單口MCBSP(Multi-Channel Buffer ed Serial Port),單周期指令執行時間10 ns,雙電源(1.8 V和3.3 V)供電,帶有符合IEEE 1149.1標準的JTAG邊界掃描仿真邏輯。

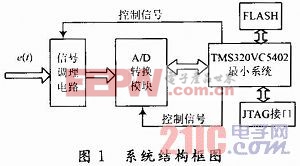

系統的結構框圖如圖1所示。系統由基于TMS320VC5402的最小系統、JTAG接口電路、FLASH存儲器、模/數轉換電路和信號調理電路構成。DSP最小系統中包括供電電路、復位電路和時鐘電路。供電電路中,將AMS1117-3.3電源轉換芯片作為5 V轉3.3 V的高性能穩壓芯片,為系統提供穩定可靠的主電源3.3 V。CX1117-1.8電源轉換芯片提供1.8 V電壓給DSP內核使用。復位電路使用高電平復位,并提供手工復位按鍵。時鐘電路采用DSP內部振蕩器方式,選用20 MHz的外部晶振。JTAG接口電路提供對DSP的內部FLASH的燒寫和仿真通信。FLASH主要用來存儲程序及初始化數據。A/D轉換模塊實現模擬信號到數字信號的轉換。

信號調理電路包括前置放大濾波電路、第二級放大電路和信號預處理電路。其中信號預處理電路使輸入的信號保持在A/D可接受的模擬輸入電壓范圍。TMS320VC5402通過編程實現對A/D等模塊的初始化和實時控制。

1.2 A/D模塊設計

系統采用的ADC芯片是TLV1578。TLV1578是TI公司專門為DSP芯片配套制作的一種8通道10位并行A/D轉換器。它將8通道輸入多路選擇器

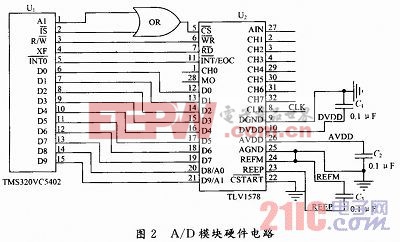

(MUX)、高速10位ADC和并行接口組合在一起,構成10位數據采集系統。器件包含兩個片內控制器(CR0和CR1),通過雙向并行端口可以控制通道選擇、軟件啟動轉換和掉電。TLV1578采用2.7~5.5 V的單電源工作,可接收0~AVDD范圍的模擬輸入電壓,具有速度高、并行接口簡單和功耗低等特性。由于TLV1578具有與DSP兼容的并行接口、內置振蕩器等特點,因此使用TLV1578時,不需要過多的外圍器件就可以方便地實現與5402連接。圖2給出了TLV1578與TMS320VC5402的連接示意圖。

DSP地址總線的A0引腳和I/O空間選擇引腳控制TLV1578的片選信號;使用DSP的XF引腳控制TLV1578的讀信號;DSP和TLV1578的數據中斷信號直接相連。

2 系統的軟件設計

2.1 程序流程

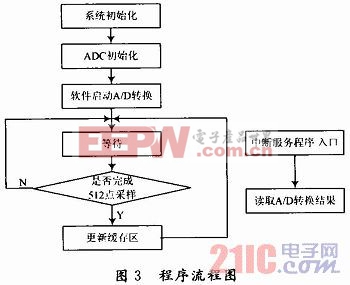

該系統對TLV1578的設置方式為:單通道輸入、軟件啟動、采用內部時鐘源、時鐘設置為20 MHz、二進制輸出方式。系統程序流程圖如圖3所示。

評論