可以將第三方的IP(來自VHDL或Verilog)吸納到NI Fl

如果適配器模塊是由NI公司開發的,那么不需要任何VHDL或其他硬件描述語言的經驗。所有的FPGA編程均通過NI LabVIEW FPGA模塊和NI-RIO驅動程序軟件以圖形化的方式完成。如果該適配器模塊是由第三方開發的,則或許提供定制的LabVIEW FPGA I/O節點。若存在一個帶有套接字的CLIP節點,用戶的體驗可能會與NI提供的解決方案相似。對于定制設計的適配器模塊,設計工程師將需要利用VHDL和XML文件創建一個帶有套接字的CLIP節點,以便在LabVIEW FPGA項目中正確表示定制的I/O。

本文引用地址:http://www.j9360.com/article/194265.htm

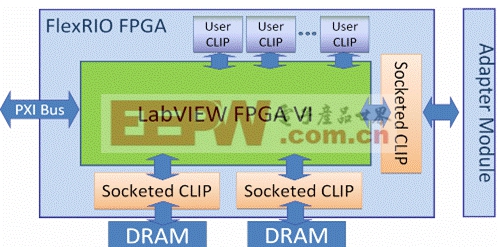

NI FlexRIO中的FPGA利用CLIP節點,集成了第三方的IP核并與適配器模塊進行通信

多年前工程師們就已經能夠將HDL代碼植入LabVIEW框圖,以運行與其LabVIEW代碼相適應的既有IP。但是,從LabVIEW 8.6 FPGA模塊開始,CLIP技術支持工程師們引入第三方的IP并與LabVIEW框圖并行執行。這樣,第三方IP核可與NI FlexRIO結合使用。

采用FPGA技術有哪些技術優勢?

下面列舉了FPGA技術的五大技術優勢。

高性能

上市時間短

低成本

高可靠性

評論