半導體功能測試基礎術語

Output Mask 輸出屏蔽,一種在功能測試期間讓測試通道的輸出比較功能打開或關閉的方法,可以針對單獨的pin在單獨的周期實施。

Output Sampling 輸出采樣,在功能測試中,DUT的輸出信號在周期內的某個時間點被評估的過程。PE卡上的比較電路會將輸出電壓和預先設定的邏輯1(VOH)和邏輯0(VOL)相比較,然后測試系統做出pass或fail的判斷。Output Sampling也稱為“Strobing”。

Test Pattern 測試向量(國內很多資料將其譯為“測試模式”),是器件一系列所設計的邏輯功能的輸入輸出狀態的描述。輸入數據由測試系統提供給DUT,輸出數據則用于和DUT的輸出響應相比較。在功能測試期間,測試向量施加到DUT并運行,當其中的一個期望輸出與器件的實際輸出不匹配時,一個failure就產生了。Test pattern也稱為“Test Vectors”或“Truth Tables(真值表)”。Test Vectors的說法更強調時序性,指邏輯電平的一系列0、1序列或其他表征。

Signal Format 信號格式,PE驅動電路提供的輸入信號的波形。

功能測試

功能測試是驗證DUT是否能正確實現所設計的邏輯功能,為此,需生成測試向量或真值表以檢測DUT中的錯誤,真值表檢測錯誤的能力可用故障覆蓋率衡量,測試向量和測試時序組成功能測試的核心。

當執行功能測試時,必須考慮DUT性能的所有方面,必須仔細檢查下列項的準確值:

VDD Min/Max DUT 電源電平

VIL/VIH 輸入電平

VOL/VOH 輸出電平

IOL/IOH 輸出電流負載

VREF IOL/IOH 切換點

Test Frequency 測試頻率/周期

Input Signal Timings 時鐘/建立時間/保持時間/控制信號

Input Signal Formats 輸入波形

Output Timings 周期內何時采樣

Vector Sequencing 向量文件的起始/終止點

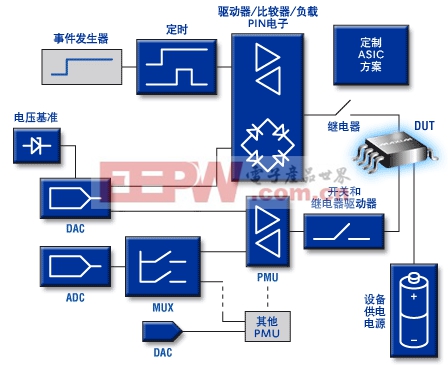

從上表可以看出,在功能測試中需要利用測試系統的大部分資源,所有的功能測試都有兩個不同的部分組成,主測試程序中的測試向量文件和指令集。測試向量文件代表需測試的DUT的輸入輸出邏輯狀態,測試程序包括控制測試硬件產生必需的電壓、波形和時序需要的信息。

評論