基于DMA的大批量數據快速傳輸模塊設計

摘要 針對Altera公司SOPC解決方案中,DMA模塊無法直接讀/寫FPGA外設的情況,提出了基于Avalon總線流傳輸模式的通用DMA讀/寫控制模塊的設計,設計了兩個自定義外設,實現了DMA對FPGA外設的高速數據存取和Nios II與FPGA大批量數據的快速傳輸。介紹了Avalon—MM總線規范,闡述了系統架構以及DMA讀控制器的設計,測試結果表明,該方法是一種高效可行的解決方案。

關鍵詞 SOPC;Nios II;DMA;Avalon總線

DMA控制器作為SOPC設計中使用頻率較高的IP核,可用于存儲器或外設間進行批量數據傳輸,以提高系統數據吞吐量。然而,由于DMA控制器只支持對基于Avalon總線流傳輸模式的外設進行數據傳輸操作,對用戶自定義外設不予支持。文中提出了一種基于Avalon總線流傳輸模式的通用DMA接口控制器設計,實現了NiosⅡ與FPGA的大批量數據快速傳輸,顯著提高了系統的數據吞吐量。

1 Avalon—MM總線規范

Avalon總線規范是為開發SOPC環境下外設而設計的,為SOPC設計者描述這些外設的端口提供了基礎。Avalon總線有多種傳輸模式,其中,流傳輸模式為從端口提供了一種機制,用于控制來自主端口的傳輸,流傳輸模式的這些特點使其特別適合于DMA傳輸。

流模式從端口傳輸模式的信號,除了在從端口傳輸中使用的信號之外,又引入了3個信號:readyfordata、dataavailable和endofpack et。其中,從端口通過設置Readyfordata有效來表示它已經準備好接收來自Avalon總線模塊的寫傳輸;使readyfordata無效表示寫操作將引起數據上溢;從端口通過設置dataavailable有效來表示它已經能夠為來自Avalon總線模塊的讀傳輸提供數據,dataavailable無效時讀操作將引起數據下溢;在任何傳輸期間,流模式從端口都可以設置endofpacket信號有效,并通過Avalon總線模式傳輸給主端口。對于endofpack et信號的解釋取決于用戶設計,必須明確外設如何響應endofpacket信號的變化。

2 系統結構

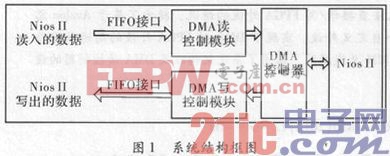

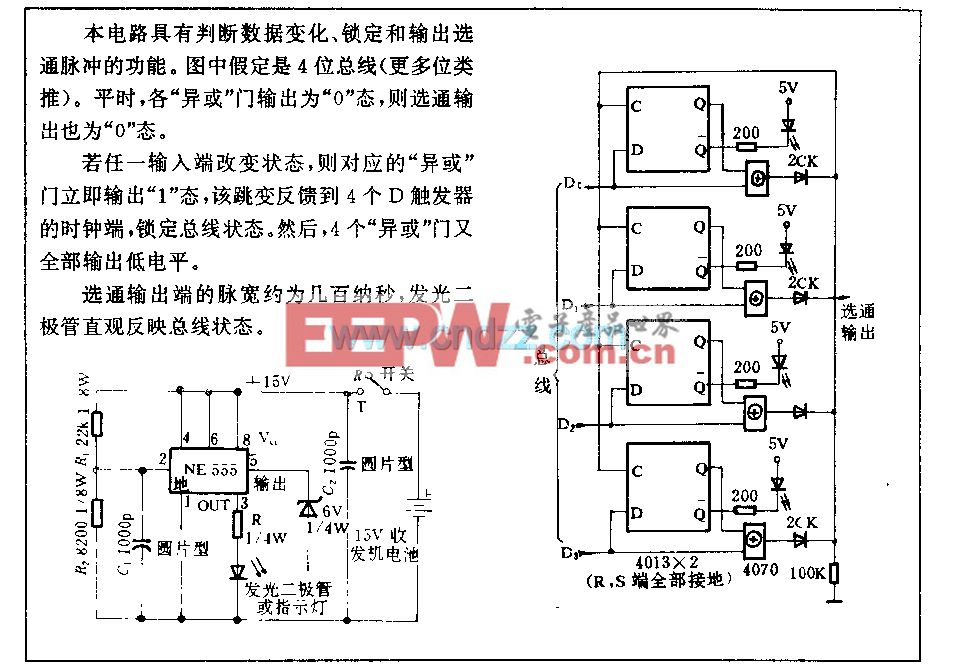

提出的NiosⅡ與外設進行大批量數據傳輸的結構如圖1所示,當NiosⅡ需要從外設讀入數據時,外設通過FIFO接口將數據寫入DMA讀控制模塊,然后數據經DMA傳輸至NiosⅡ,反之,當NiosⅡ輸出數據時,數據通過DMA傳輸至DMA寫控制模塊,FPGA邏輯通過FIFO接口從這個模塊讀取數據。DMA讀/寫控制模塊的設計,是為了解決SOPC中DMA模塊與FPGA片上FIFO不同接口間的數據傳輸問題,而在SOPC中,DMA模塊使用的是支持流傳輸模式的Avalon—MM總線。DMA讀/寫控制模塊主要完成兩個功能:一是FIFO與DMA主端口之間的數據交互;二是作為一個NiosⅡ的外設,NiosⅡ處理器能夠對此外設進行控制并能隨時獲取該外設的狀態信息。

3 DMA讀/寫控制模塊的設計

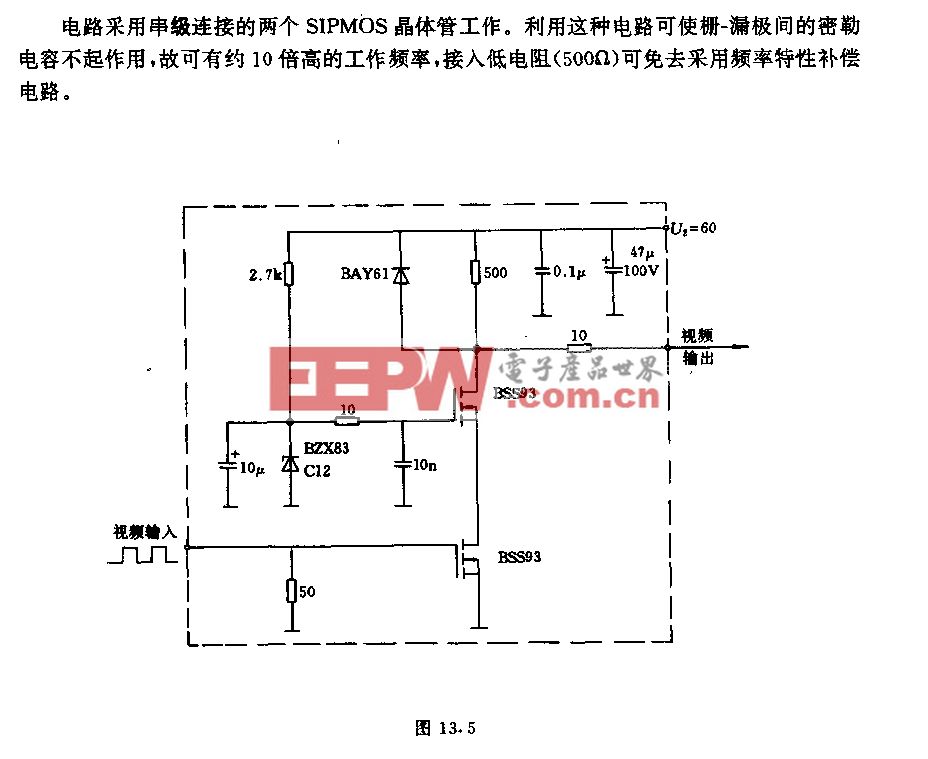

DMA讀/寫控制模塊作為系統結構的核心,其結構框圖如圖2所示。此模塊包括兩個Avalon—MM從端口:一個作為DMA從端口,用于處理DMA對此模塊的數據讀操作;另一個Avalon—MM從端口是NiosⅡ的控制從端口,用于NiosⅡ處理器對這個模塊進行控制并且隨時獲取此模塊的狀態信息。模塊還包括一個中斷請求信號(IRQ),當外設有數據需要讀取時,可以使這個信號有效,從而通知NiosⅡ發起DMA讀傳輸。另外,DMA讀控制模塊中還例化了一片FPGA片上FIFO作為數據上傳FIFO,用于系統待上傳數據的暫存。使用FIFO可以提高數據傳輸的吞吐量,同時簡化FPGA硬件邏輯的操作,圖2中的管道(Conduit)端口就是FPGA硬件邏輯操作FIFO的接口。

評論