基于SOPC的簡易誤碼率測試儀設計技術

本設計主要用于石油勘探儀器車與外部設備連接電纜的通信可靠性測試。誤碼率測試儀主要由測試信號發生模塊、收發模塊、誤碼統計模塊以及鍵盤和液晶顯示模塊等部分組成。通過對測量參數的設置,該設備可以對通信線路進行不同速率、不同碼元的誤碼率閉環測量,并通過圖形點陣顯示屏進行實時顯示,以供評估使用。

常見的誤碼率測試儀多數專用于測試各種標準高速信道,不便于測試實際應用中大量的專用信道,并且價格高,搭建測試平臺復雜。隨著大規模集成電路的迅速發展,FPGA在保持其集成度高、體積小、功耗低、性價比高等特點的同時,能夠實現越來越復雜的功能,廣泛應用于通信設備的設計實現。本設計采用Altera公司的Cyclone系列FPGA芯片EPlCl2,內嵌Nios II軟核CPU,并利用SOPC技術進行了整體設計,在保證具有良好性能的同時,更有利于后期的優化和升級。接口采用ECL(電流開關型邏輯電路)電平,可以直接鏈接測試電纜,方便現場測試。

1 SOPC和Nios II概述

SOPC(System On Programmable Chip,可編程片上系統)是基于大規模FPGA的單片系統,是美國Altera公司于2000年提出的(同時推出了相應的開發軟件QuartusII)。SOPC的設計技術是現代計算機輔助設計技術、EDA技術和大規模集成電路技術高度發展的產物。SOPCBuilder是Altera公司為硬件設計人員開發的一套系統級硬件設計工具,通過它可以方便地創建Nios II CPU系統級設計項目,從而為設計人員提供SOPC設計必需的軟硬件設計平臺。

Nios II嵌入式處理器是FPGA生產廠商Altera公司推出的軟核CPU,是一種面向用戶的、可以靈活定制的通用精簡指令集架構(RISC)32位高性能嵌入式CPU。NiosII以軟核的方式提供給用戶,并專門為在Altera的FPGA上實現做了優化,用于SOPC集成,最后在FPGA上實現。Nios II IDE是SOPC系統的軟件開發環境,在Nios II IDE中可以進行軟件的編寫、下載和調試等工作。

2 誤碼率測試儀功能概述

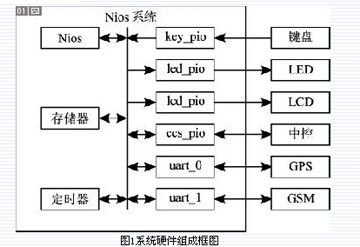

誤碼率測試儀分別設有2個通信測試端口――輸出端口和輸入端口,分別連接到待測試電纜的兩端,構成數據傳輸回路。FPGA內部有一個Nios II軟核CPU,負責初始化和管理該系統;用VHDL語言編寫了收發芯片AM7968和AM7969的控制器接口模塊,完成測試碼發送、接收、誤碼率統計的任務;系統還設有4×4的矩陣掃描鍵盤和128×64分辨率的0LED圖像點陣顯示屏作為人機接口,如圖1所示。

用戶通過矩陣鍵盤輸入并設置測試代碼、通信速率以及測量模式(定時測量、定量測量)。確認開始測量后,Nios配置AM7968和AM7969,并通過AM7968發送測試代碼,經待測試電纜及AM7969接收到數據后,將接收的代碼與原始數據比較。如果發現不等,即認為是誤碼,統計誤碼個數的計數器加1。當測量停止時,0LED顯示屏輸出誤碼率數值及其他測量信息。

3 硬件設計

3. 1 收發模塊設計

誤碼率測試儀的收發芯片采用的是美國AMD公司的AM7968和AM7969。

AM7968發送端芯片和AM7969接收端芯片提供通過同軸電纜或者光線傳輸的一般通用接口,通信速率在40~175 Mbps的范圍內可以調節。AM7968/AM7969為并行TTL總線接口,一共有12位的數據和控制總線,可以靈活配置成8~10位數據總線,對應4~2位控制總線的接口形式。

(1)發送端設計

如圖2所示,芯片AM7968是信號的發送端。根據功能設置,測試代碼的發送模式有固定代碼模式、循環碼模式和自定義代碼模式3種。故設置控制寄存器(mode_reg)位寬為2:OO為初始狀態,系統位于初始化狀態;01為固定代碼模式,發送系統預設的代碼;lO為循環代碼模式,測試代碼從00h~FFh連續循環發送;11為自定義代碼模式,發送用戶自定義的代碼。

發送頻率的設置,是通過AM7968的輸入時鐘(50MHz)直接分頻實現的。在AM7968的控制器中,設有時鐘分頻寄存器(clk_div_reg)。該寄存器位寬為8。也就是說,用戶可以在40~175 Mbps范圍之內,設定256種不同頻率,進行誤碼率的測試工作,盡可能地滿足用戶的測試頻率要求。

評論