基于FPGA器件的Sobel算法實現

2.2系統實體設計本文引用地址:http://www.j9360.com/article/192125.htm

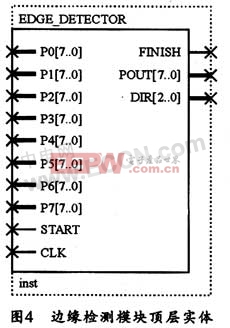

依據上述設計思路,可以設計出如圖4所示的邊緣檢測模塊的頂層實體。其中START為來自外界的檢測啟動信號輸入,用于啟動邊緣檢測;CLK為時鐘信號輸入,是狀態機的驅動時鐘;數據輸入端口P0~P7分別接收像素窗中相應像素的8位灰度值;POUT為檢測結果灰度輸出,輸出0表示非邊緣像素,輸出255表示邊緣像素;DIR為方向輸出;FINISH為檢測結束信號輸出,用于配合其它模塊協同工作。

2.3系統行為描述

由于設計采用行為建模,因此,系統描述不涉及任何硬件器件以及連接相關,只需在結構體中設置兩個進程來描述狀態機,并定義相關變量和函數就可以完成對此系統的描述。

為描述系統行為,首先應定義如下信號:

其中,信號ST表示狀態機狀態;HF、VF、LF、RF分別用于存儲四個方向濾波值;MAG存儲依據四個濾波值得出的梯度幅度值。

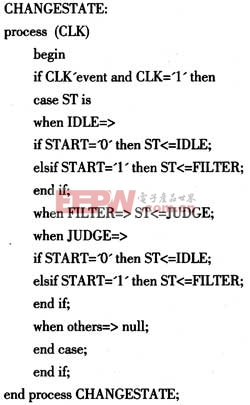

進程CHANGESTATE可完整描述狀態圖中各狀態間的轉移關系。此進程由敏感信號CLK進行驅動,并在時鐘上升沿到來時,可通過判斷當前狀態以及相關轉移條件來確定狀態機的次狀態。其完整的代碼如下:

進程STATEBEHAVIOR主要負責處理狀態機特定狀態下的行為輸出。此進程由狀態信號ST作為敏感信號進行驅動。在空閑態(ST=IDEL)時,系統初始化相應輸出;而在濾波態(ST=FILTER)時,系統則調用四個函數H_FILTER ()、V_FILTER()、L_FILTER()和R_FILTER()并依照Soble算法進行濾波計算;決斷態(ST=JUDGE)時,則調用函數MAGNITUDE ()和PHASE ()來計算梯度的大小和方向,并通過決斷后輸出處理結果,同時使檢測結束信號有效(FINISH='1')。其完整代碼如下:

評論