1553B總線遠程端點數據鏈路層協議的FPGA實現

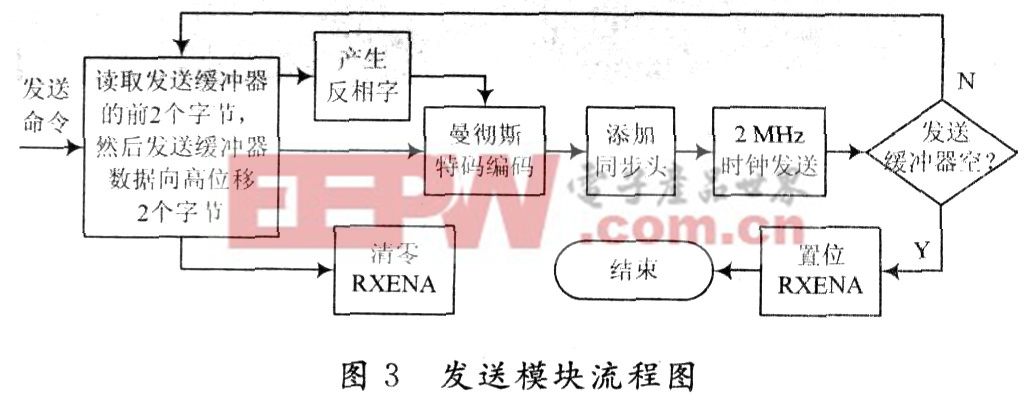

命令解析完成后都需要進行狀態反饋或者數據發送,而完成這個功能的是發送模塊,發送模塊負責把命令解析模塊和接收模塊裝載到發送緩沖器中的數據發送到總線上去,如圖3所示,它包括讀取數據,產生反相字,曼徹斯特碼編碼,添加同步頭,2 MHz時鐘數據發送等幾個部分,同時由于發送緩沖器中數據有可能多于2個字節,因此還可能需要循環進行這個操作。下面就根據發送的具體流程設計每個部分。首先是發送緩沖器部分,當接收到發送命令后,發送模塊就第一次讀取發送緩沖器的前兩個字節,因為這兩個字節肯定是狀態字,然后把這兩個字節貼上狀態字標簽,繼續傳給后繼單元,待完成以后就把接收發送緩沖器的發送數據長度寄存器減1,并把發送緩沖器中的數據向前移動2個字節。如果發送數據長度寄存器不為零,則繼續等待下一次的發送。

本文引用地址:http://www.j9360.com/article/192062.htm

本文引用地址:http://www.j9360.com/article/192062.htm2.4 上層交互模塊

最后一個模塊是上層交互模塊,這個模塊負責與上層微控制器進行信息交互,它負責把微控制器寫入的數據放入相應的寄存器中,或者按上層微控制器的命令回傳相關的數據。上層交互模塊主要包括邊沿信號與電平信號轉換、地址解碼和讀寫寄存器。因為協議實現模塊中采用的是邊沿信號觸發,而上層微控制器給FPGA的信號是電平信號,要順利地完成通信,就需要進行轉換,這里通過鎖存器和計數器來完成。地址解碼就是把收到的地址解碼成相應寄存器的地址,然后寫入收到的數據或者把寄存器中的數據讀出放入到數據總線上。

3 仿真及FPGA實現

為了確保設計的可行性,必須對設計進行時序仿真。整個協議VerilogHDL實現程序在Altera公司的FPGA開發軟件QuartusⅡ中編寫、編譯、綜合。整個程序的仿真在Modelsim 6.0中進行,其仿真過程如下:

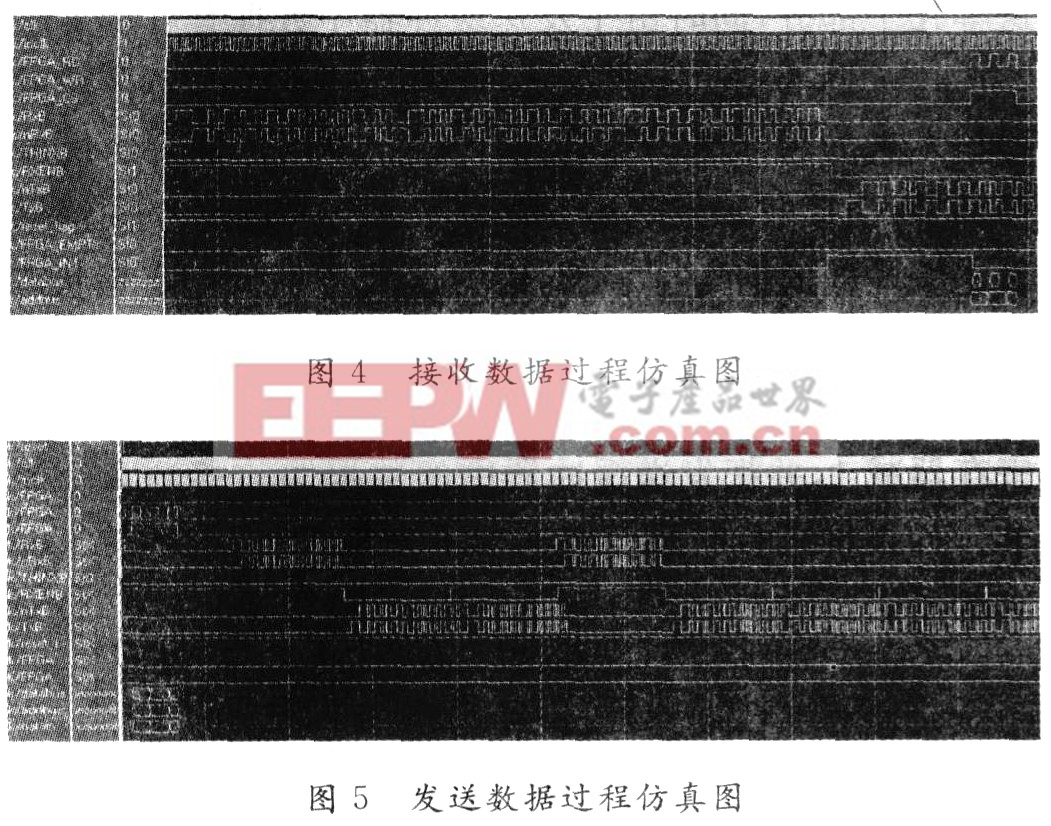

(1)接收數據。總線控制器發送給實現程序兩個數據:0x1234和Ox5678,上層微控制器在實現程序接收數據后通過上層交互模塊把數據讀出,其中第一個數據包含了接收數據長度,通過圖4可以看出整個過程順利進行,完成了預定目標。

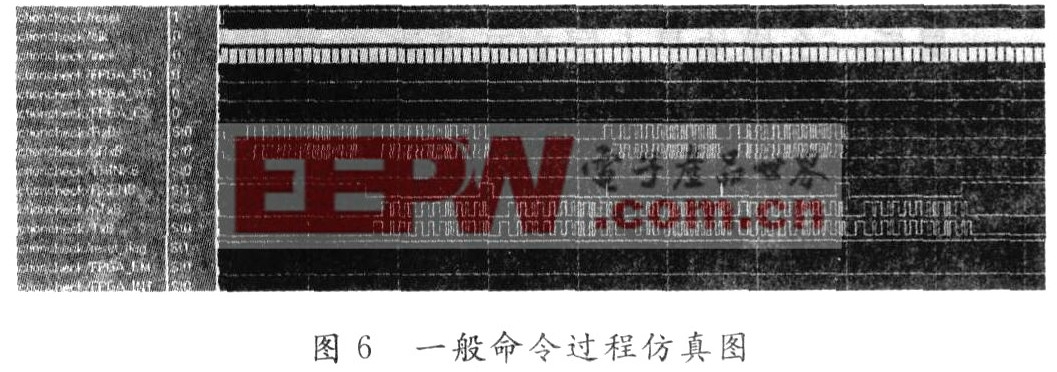

(2)發送數據。總線控制器間隔地發送給實現程序兩個發送數據的命令,讓實現程序反饋相關的數據,這些數據是通過上層交互模塊提前寫入到實現程序中的,其仿真過程如圖5。通過圖5也可以看出在實現程序接收到命令到發送出數據的延時時間大約為4μs,完全符合1553B總線對遠程端點反饋信號延時的規定。

(3)一般命令。總線控制器發送給實現程序一般的方式代碼命令,代碼分別為:000ll,10010,01111和00001,其仿真過程如圖6所示。可見,實現程序正確地反饋了相關信息,符合設計要求。

評論