1553B總線遠程端點數據鏈路層協議的FPGA實現

(7)自測結果寄存器(STRR):STRR用于存放上次自測的結果。為了方便地址分配,設計中把發送和接收FIFO都作為一個16位寄存器來對待。本文引用地址:http://www.j9360.com/article/192062.htm

2 1553B遠程端點數據鏈路層協議的FPGA實現的總體設計

1553B遠程端點數據鏈路層協議的FPGA實現一共分為4個模塊:序列解析模塊、命令解析模塊、發送模塊和上層交互模塊。整個協議實現采用時序驅動的方式進行,時鐘頻率為8 MHz,下面就按照數據進入的順序介紹整個協議的FPGA實現過程。

2.1 序列解析模塊

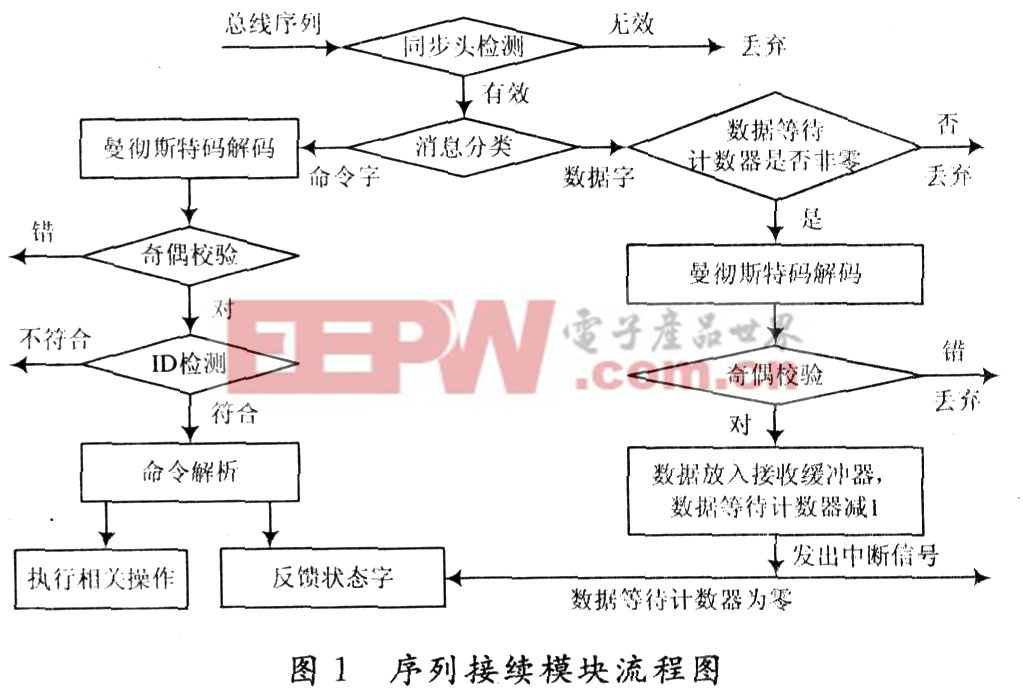

這個模塊接收從收發器接收的信號序列,先后進行同步頭檢測,曼碼解碼,奇偶校驗,ID檢測等步驟,最后給命令解析模塊一個只包含命令信息的16位數據,以及其字特性。其實現流程如圖1所示。

序列解析模塊首先對進入的總線序列進行同步頭檢測,如果有效,則進行曼徹斯特碼解碼。曼徹斯特碼解碼是在同步頭檢測有效時同步開始的,它在同步頭檢測有效后每隔1 000μs對序列采樣一次,并把采樣值作為解碼值,同時判斷在采樣時序列是否發生了跳變,如果發生,則說明序列滿足曼徹斯特碼編碼,否則認定序列存在編碼錯誤,停止解碼并置位錯誤寄存器,而第一次采樣是在同步頭檢測有效后250ns。解碼完成后進行奇偶校驗,接收模塊對有效序列進行奇偶校驗,如果奇偶校驗錯誤,則丟棄這個序列,同時置位消息差錯位;如果奇偶校驗正確,則進入ID檢測部分。奇偶校驗在VerilogHDL中通過位異或就可以實現。

當奇偶校驗正確以后,接收模塊就根據從同步頭檢測得到的字類型進行不同操作。對于數據字,接收模塊收到序列后就檢測等待數據字寄存器的值,如果不為零,則把這個數據放入到接收緩沖器中,如果等待數據字寄存器的值為1,則首先把寄存器清零,然后把中斷請求信號置位,最后把狀態寄存器的值放入發送緩沖器中,并通知發送模塊發送以及復位等待數據字寄存器,否則把等一待數據字寄存器的值減1,等待下一個字的到來。如果等待數據字寄存器值為零,則認為傳輸錯誤,丟棄這個數據字。對于命令字,接收模塊進行ID驗證,檢查所收到的命令是否是總線控制器發給本節點的。它提取所收到的16位有效信息序列中的高5位,與本節點的ID比較,如果不相同,則丟棄這個序列,等待下一個序列的到來;如果相同,則表示這個序列是總線控制器發給本節點的命令,保存命令,啟動命令解析模塊。

2.2 命令解析模塊

命令解析模塊完成對收到的命令字進行解析,對收到的數據進行存儲的工作。命令解析模塊是整個協議的核心,它負責把總線控制器傳給本節點的命令翻譯成本節點的操作,并執行相關動作。其工作流程如圖2所示。

假設命令字存放在寄存器CMD―REG[15:0]中,則命令解析模塊首先檢測CMD REG[9:5],如果CMD REG[9:5]不為全1或者全0,就表示總線控制器給節點的是數據傳輸命令;命令解析模塊則繼續檢測CMD REG[10]位,如果為1,則表示總線控制器要求本節點發送數據,同時用CMD REG[4:0]指定了需要發送的數據長度;命令解析模塊在收到這個命令后就把相關的數據和狀態寄存器的值裝入發送緩沖器中,并通知發送模塊進行發送。如果CMD REG[10]位為O,則表示總線控制器要求本節點接收數據,同時也用CMD REG[4:0]指定了接收數據的長度,而用CMD REG[9:5]指定了數據接收子節點的ID,命令解析模塊在收到這個命令以后就把CMD REG[4:O]裝入等待數據字寄存器中,等待后繼數據字的到來。如果CMD REG[9:5]為全1或者全O,則表示總線控制器傳輸的控制命令字,并通過CMD REG[4:0]指定了相應的命令方式代碼。對于命令方式代碼,命令解析模塊根據1553B總線標準對不同方式代碼進行相關的寄存器置位操作。

2.3 發送模塊

評論