基于CPLD的鍵盤控制器設計

0 引 言

由于CPLD的可再編程性質,可以將同一裝置用于不同的鍵盤和產品,而收到高產量、低成本的效果,同時也節約了單片機的資源以做它用。可再編程的特點輔之簡便易用的設計工具,使設計可以進行晚期更改,提高了產品設計的靈活性,降低了風險。在單片機應用系統中,利用鍵盤接口輸入數據,是實現現場實時調試、數據調整和各種參數設置最常用的方法。單片機的外圍鍵盤擴展電路有多種實現方式,例如直接利用單片機的I/O接口,或者采用8255A接口芯片,就可以實現外圍鍵盤的擴展功能。但是,在這些方法中,鍵盤擴展電路需要占用單片機的資源對按鍵進行監控和處理,這對要求高實時性處理的單片機系統是不容易實現的。為了解決這一問題,可以使用專用鍵盤接口芯片來擴展鍵盤子系統。但是這類專用鍵盤接口芯片在使用靈活性方面尚有欠缺,尤其當用戶需要實現某些特定功能時,其缺點更為明顯。針對上述問題,在此提出一種基于Lattice公司LC4128V的4×4鍵盤接口芯片設計。采用的軟件開發環境是IspLEVER。

l 開發環境介紹

IspLEVER是Lattice公司最新推出的一套EDA軟件。設計輸入可采用原理圖、硬件描述語言、混合輸入3種方式,它能對所設計的數字電子系統進行功能仿真和時序仿真。編譯器是此軟件的核心,能進行邏輯優化,將邏輯映射到器件中去,自動完成布局與布線,并生成編程所需要的熔絲圖文件。軟件中的Constraints Editor工具允許經由一個圖形用戶接口選擇I/O設置和引腳分配。lspLEVER軟件提供給開發者一個簡單而有力的工具,用于設計所有Lattice可編程邏輯產品。

2 鍵盤控制器設計

2.1 基于LC4128V的4×4鍵盤控制器設計

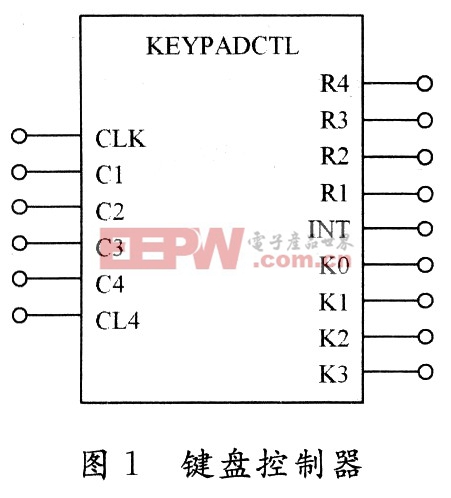

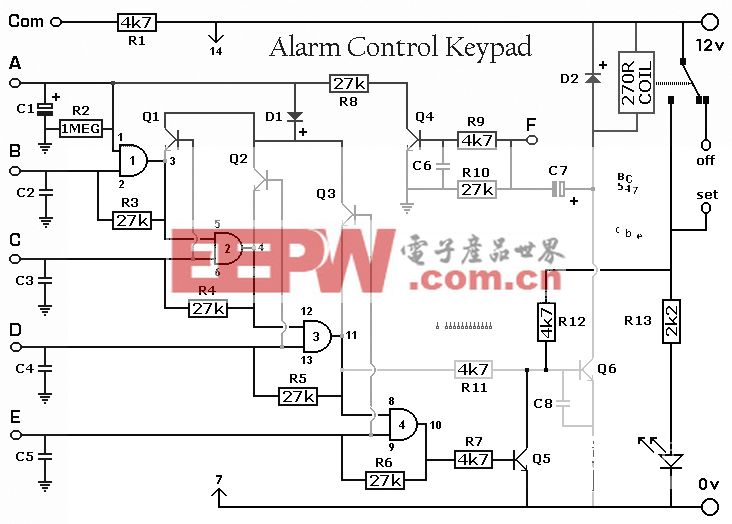

圖1給出基于Lattice公司的可編程邏輯器件LC4128V的4×4鍵盤控制器(KEYPADcTL)設計。

根據鍵盤的掃描原理,鍵盤控制器的輸出引腳R1~R4(行掃描線)依次循環輸出低電平,并將相應的鍵盤行置低。當有按鍵按下時,相應的輸入c1~c4(列回復線)也被置低。然后根據行和列的低電平對應關系就可以通過編碼確定按下的鍵值。輸出K0~K3就是最終等待單片機讀取的鍵值。INT輸出單片機的中斷信號,通知單片機來讀取鍵值。CLK是控制器的時鐘信號,cLR是控制器的清零復位信號。

2.2 內部原理圖及其主要部分的工作原理

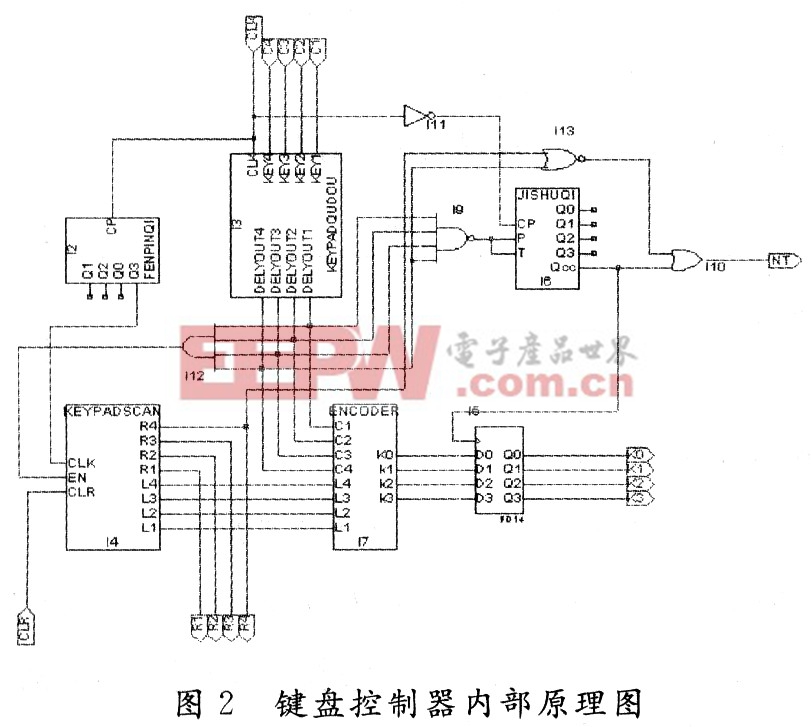

鍵盤控制器內部由鍵盤掃描電路、編碼器電路、鍵盤去抖動電路、分頻器電路、計數器電路和鍵值鎖存器組成,如圖2所示。

(1)鍵盤掃描電路是一個能自啟動到所需要狀態的狀態機,當系統上電并同時輸入一個有效的復位清零信號CLR后,掃描電路輸出端R1~R4(L1~L4)則依次按照設計要求循環輸出以下掃描電平1110,1101,1011,0111。L1~L4作為編碼器的輸入,通過與列回復線(C1~C4)的對應關系參與編碼。然而R1~R4是將L1~L4加上高電平使能三態門輸出的鍵盤行掃描線。將行掃描線加上三態門輸出,是為了防止當一列上的2個或更多按鍵被同時按下時,將使LC4128V的引腳高低電平短接,如果這種情況發生,不但影響鍵盤控制器的準確性,更嚴重的是會燒壞可編程邏輯器件LC4128V,所以該控制器通過三態門輸出行掃描線。三態門的使能信號就是其通過的信號取反,這樣輸出的高電平將為高阻狀態。通過對鍵盤的行線分別接個上拉電阻便可得到與L1~L4一樣的輸出信號。

評論