EZ-USB FX2的數據采集和傳輸系統設計

FPGA提供TLC5510 20 MHz的工作時鐘和使能輸出信號OE,低電平有效,同時接受TLC5510的采樣數據。由于系統需要同步的兩路采樣,所以由FPGA輸出的時鐘和使能輸出信號OE同時控制2個TLC5510。這樣FPGA就可以同時收到兩路同時采樣的信號數據,將其存入兩個獨立的異步FIFO中。

值的注意的是,實驗中將FPGA產生的工作時鐘和使能輸出信號先輸入74HCT573,然后由74HCT573的輸出去控制兩路的TLC5510。這主要是完成將FPGA的CMOS電平轉換成TTL電平的工作。在實驗的初期,未經過電平轉換的信號在控制TLC5510時,得不到穩定數據。后來經過改善后,TLC5510能夠穩定、準確地完成采樣和數據輸出。

(2)數據傳輸模塊

在數據傳輸模塊中,為了保證較高的傳輸速度,使用不經過CPU的SLAVEFIFO控制工作模式。模塊的基本工作過程為:當A/D采樣數據存儲滿FPGA中的FIFO后,FPGA根據SLAVEFIFO的控制時序產生相應的控制信號,將在FIFO中的數據傳輸給EZ-IJSB FX2的內部端點FIFO,而當內部端點存儲滿后,FX2自動將數據傳輸到上位機。外部控制器FPGA對FX2的控制進程如下:

①IDLE,當寫事件發生時,轉向狀態1。

②狀態1,指向EZ-LJSB FX2的內部端點IN FIFO,激活FIFOADR[1:0],轉向狀態2。

③狀態2,如果內部端點FIF0滿標志為“假”(FIFO不滿),則轉向狀態3;否則停留在狀態2。

④狀態3,傳送總線驅動數據。產生一個SLWR跳變,轉向狀態4。

⑤狀態4,如果有更多的數據要寫,則轉向狀態2;否則,轉向IDLE。

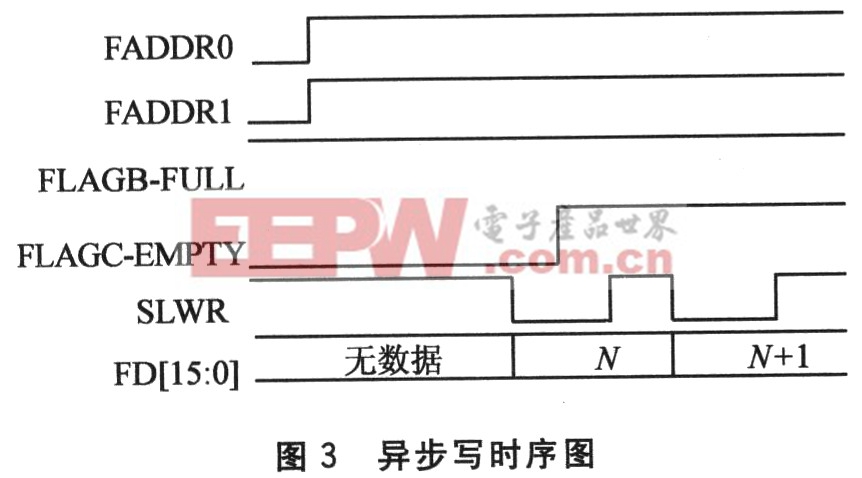

EZ-JSB FX2內部端點FIFO異步寫的時序如圖3所示。

2 FPGA的模塊設計

在系統中,FPGA構成了數據采集系統和數據傳輸系統的“橋梁”,完成對TLC25510的控制和數據的存儲,同時也完成對EZ-USB FX2單片機的控制。利用FPGA強大的功能,使電路的結構得到了簡化,不需要利用分立器件來完成對數據的存儲。因此,在FPGA中需要構成4個模塊:2片FIFO數據存儲模塊、數據通道選擇模塊、控制模塊和輸出20 MHz時鐘的PLL模塊。

(1)2片FIFO數據存儲模塊

FIFO數據存儲模塊主要完成對A/D轉換數據的存儲。由于需要兩路同時采集數據,所以要有2個FIFO模塊,這樣易于對數據的存儲和傳輸控制。每個FIFO存儲模塊的存儲容量定為2 048 B,可通過MegaWizard工具來調用。

(2)數據通道選擇模塊

數據通道選擇模塊主要是針對兩路的數據讀取和傳輸而設計的。當A/D轉換器采集到對應的數據后,存入兩個異步FIFO存儲模塊中。在兩個異步FIFO存儲模塊存儲滿后,對FIFO存儲模塊數據的讀取是關鍵。數據通道選擇模塊的基本原理是在控制模塊對讀取數據進行計數,當把其中的一個FIFO存儲模塊讀取完后,由控制模塊發出通道切換信號,由數據通道選擇模塊切換數據通道,再讀取另一個FIFO存儲模塊的數據。

(3)控制模塊

控制模塊要完成對TLC5510、FIFO存儲模塊、數據選擇模塊和EZ―USB FX2的控制,這是整個系統的關鍵。根據系統實現的功能和各個模塊的控制時序,控制模塊將產生相應的控制信號,實現系統的采集和存儲的功能。

(4)20 MHz時鐘的PLL模塊

系統提供的FPGA外部時鐘頻率為50 MHz,而TLC5510的最大采樣工作頻率為20 MHz。所以通過對前置分頻參數N=5、倍頻器參數M=2的設置,將50 MHz鐘頻率分頻成20 MHz的時鐘作為采樣時鐘和系統的工作時鐘。

3 EZ―USB FX2的固件設計

固件程序是指運行在設備CPU中的程序。只有在該程序運行時,外設才能稱為具有給定功能的外圍設備。C2ypress公司為FX2固件開發提供了一個固件庫和固件框架,都是在Keil C51集成開發環境下開發的。固件庫提供了一些常量、數據結構、宏、函數來簡化用戶對芯片的使用。固件框架實現了初始化芯片、處理USB標準設備請求以及掛起狀態下的電源管理等功能。該框架不添加任何代碼,編譯后生成的.HEX文件載人芯片就能和主機進行基本的USB通信。用戶主要的工作就是選擇適合的傳輸方式,添加需要使用的端點,在框架預留的地方(如TD_Init()、TD_Poll()等函數中)添加初始化代碼和完成特定功能的代碼。這樣大大簡化了用戶對程序的編寫,在不十分了解USB2.O協議的情況下,也能通過代碼的編寫,實現USB的傳輸功能。

評論