改進型CIC抽取濾波器設計與FPGA實現

摘 要:為了改善級聯積分梳狀(CIC)濾波器通帶不平和阻帶衰減不足的缺點,給出一種改進型CIC濾波器。該濾波器在采用 COSINE濾波器提高阻帶特性的基礎上,級聯了一個SINE濾波器,補償了其通帶衰減。硬件實現時,采用新的多相分解方法結合非遞歸結構,不僅大大減少了存儲單元數量,還使電路結構更加規則。經仿真和FPGA驗證,改進型CIC濾波器使用較少硬件,實現了阻帶衰減100.3 dB,通帶衰減僅為O.000 1 dB 。

關鍵詞:CIC抽取濾波器;COSINE濾波器;SINE濾波器;設計優化;FPGA

抽取濾波器是∑-△模/數轉換器中的重要組成部分,積分梳狀濾波器經常作為第一級濾波器,用以實現抽取和低通濾波。其優點是實現時不需要乘法器電路,且系數為整數,不需要電路來存儲系數,同時通過置換抽取可以使部分電路工作在較低頻率,與相同濾波性能的其他FIR濾波器相比,節約了硬件開銷。經過仿真,抽取率為32的一階積分梳狀濾波器第一旁瓣相對于主瓣的衰減最大約為15 dB,這樣的阻帶衰減根本達不到實用濾波器的設計要求。為了改變濾波性能,一般采用級聯積分梳狀濾波器(CIC)。但經過CIC降頻濾波系統降頻后會產生信號混疊現象,并且主瓣曲線不平,需要用新的算法或新結構來修正改善這些特性。

1 CIC抽取濾波器原理

經典的抽取濾波器為Hogenauer CIC濾波器,其傳輸函數表達式為:

式中:參數M為降頻因子,決定了CIC的通帶大小;K為濾波器的階數,對阻帶衰減起到加深作用。頻率響應為:

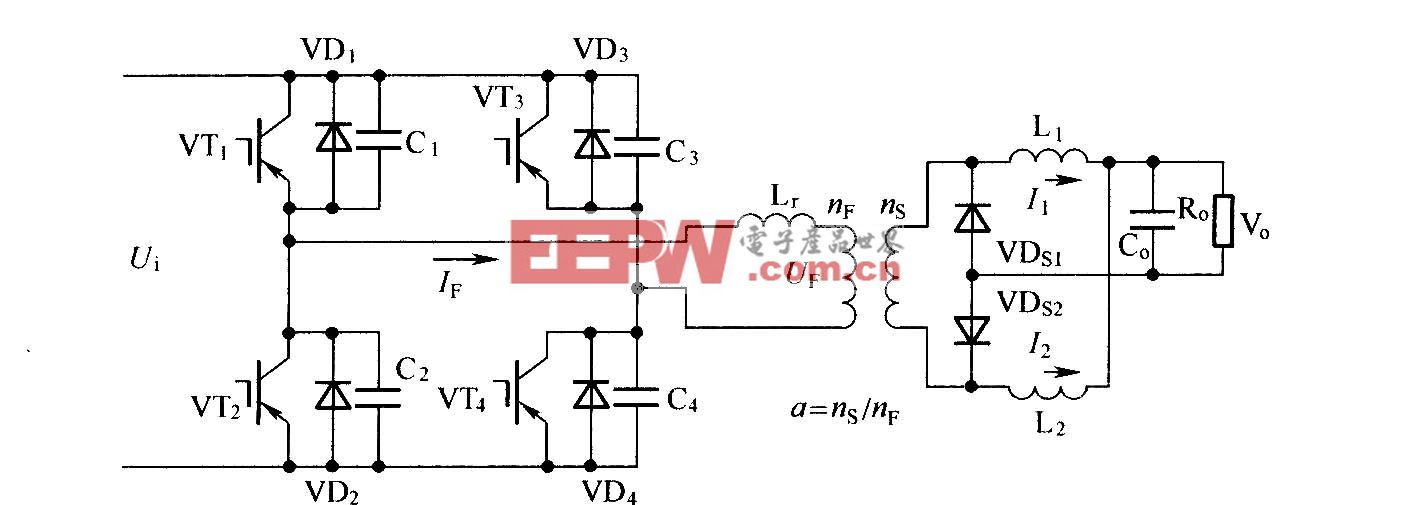

濾波電路由積分模塊與差分模塊組成,根據置換原則將抽取因子提到差分模塊之前,使其工作在較低頻率,并節省了M-1個存儲單元,框圖如圖1所示。

2 改進的CIC結構

為了改善CIC抽取濾波器阻帶衰減不足的缺點,采用一種新型COSINE濾波器,其傳輸函數為:

當N取不同值時,幅頻響應如圖2(a)所示。

把不同N值的COSINE濾波器級聯,幅頻響應會呈現低通特性,因此文獻[4]采用CIC濾波器級聯COSINE濾波器的結構來改善傳統CIC濾波器的幅頻特性。令Ni=M/2i+1,此時COSINE濾波器第一個零點與CIC濾波器的第一個零點重合,增加了第一個零點附近旁瓣的衰減。取M=32,傳輸函數為:

![]()

評論