基于FPGA的UART設計實現及驗證

通用異步收發器(Universal Asynchronous Receiver Transmitter,UART)是數字通信領域流行和廣泛使用的一種接口設備,主要用來控制符合RS 232-C協議的計算機與串行設備間的通信。普通串行外設和計算機間的通信,一般使用通用的串行接口芯片,但是這種接口芯片存在體積較大、接口復雜以及成本較高的缺點,會使得硬件設計更加復雜,并且結構與功能相對固定,無法根據設計的需要對其邏輯控制進行靈活的修改。而目前日趨成熟的SOC技術則要求將整個設計的功能集成在單片或幾塊芯片當中,因此,將UART的功能集成在FPGA芯片當中,可以使整個系統更為靈活、緊湊,性能也更加穩定。本文提出了一種使用VHDL語言開發UAWT的方法,實現了FPGA與計算機之間的數據通信,并將其應用于FPGA芯片開發的功能驗證當中,從而衍生出了將UART嵌入到EPGA芯片,與計算機互聯的一種直觀的FPGA設計的驗證和調試方法。

本文引用地址:http://www.j9360.com/article/192001.htm1 UART通信原理

UART采用通用的RS 232-C串行接口標準,該協議的優點是使用廣泛,幾乎所有計算機和串行外設當中都置有這種接口,其傳輸距離可達15 m,并且實現較簡單,用于雙向連接時最少只需要2條導線即可實現基本通信。UART的具體幀格式如圖1所示,每幀數據由開始位、數據位、奇偶校驗位和停止位四部分依次組成。其中,開始位為低電平;數據位長度為5,6,7,8不等;奇偶校驗的模式有無校驗、奇校驗、偶校驗、粘附校驗1和粘附校驗0;停止位為高電平,具體長度為1位、1.5位和2位不等,這些選項都通過UART內部的線性控制寄存器來確定。當沒有數據發送時,發送和接收引腳都保持高電平。

2 UART的FPGA實現

本實現中,UART主要包括接收模塊、發送模塊、MODEM控制器和中斷仲裁4個部分。它們的具體功能如下:

接收模塊 具體作用是接收從串行數據輸入端口SIN送來的異步數據,并進行串/并轉換,此外,接收模塊還包含模塊控制和模塊狀態配置功能,用來設置接收數據幀的屬性以及向中斷仲裁模塊輸出狀態信號;

發送模塊 其作用是對從CPU送來的并行數據進行并/串轉換,將串行數據從SOUT輸出到串口,同接收模塊相同,該模塊也包含模塊控制和模塊狀態配置功能;

中斷仲裁模塊 其作用是用來實現外部接口對內部寄存器的操作以及中斷信號的仲裁操作,在UART的工作過程中,發送和接收模塊的狀態信號都送入該模塊的線性狀態寄存器中,經過內部的邏輯操作輸出相應的中斷信號,指示與UART相連的外部設備進行相應的讀寫操作;

MODEM模塊 其作用是用來和外部的調制解調器或者其他的UART設備進行通信。

2.1 接收模塊

在接收的過程中,由于串行數據幀異步于接收時鐘,因此,當檢測到SIN由高電平到低電平的變化將被認為是一幀數據的開始位。為避免由于噪聲引起的錯誤數據,本設計中實現了錯誤開始位檢測功能,即要求開始位必須在收發波特率時鐘的50%以上為低電平。由于我們采用的內部時鐘其頻率是波特率時鐘的16倍,因此開始位至少在8個內部時鐘周期內為低電平才被認為有效。一旦開始位被確認,后面的數據比特和校驗比特將會每16個內部時鐘周期采樣一次。

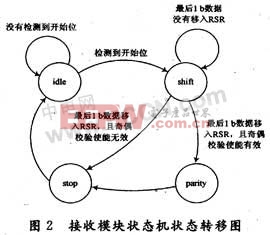

接收模塊包括一個數據緩沖寄存器和一個接收移位寄存器。當檢測到開始位有效時,其后的數據比特將會依次存人數據移位寄存器,根據數據幀的配置,當接收完所有數據比特后會根據奇偶校驗是否被使能來判斷下一步進行校驗或停止接收,等待外部設備讀取接收到的數據。整個過程可通過狀態機方便的實現,狀態轉移圖如圖2所示。

由圖2不難看出,接收模塊的狀態機包含4個狀態:空閑狀態(idle)、移位狀態(shift)、奇偶校驗狀態(parity)和停止位狀態(stop)。其工作過程如下:當系統復位時,狀態機進入idle狀態,等待開始位,SIN由高電平變為低電平并被確認為有效的開始位后,狀態機進入shift狀態;shift狀態中,接收模塊為每一個數據比特移人等待16個內部時鐘周期,接收完一幀數據后,若奇偶校驗使能有效,跳轉到parity狀態,否則,進入stop狀態;在parity狀態中對奇偶校驗比特進行采樣,狀態機將跳轉到stop狀態;狀態機進入stop狀態后,等待16個內部時鐘周期后將對停止位的長度進行采樣,而后進人idle狀態。

2.2 發送模塊

在發送過程中,當發送數據裝載到發送保持寄存器后,串行數據將自動使能從而進行數據傳輸。首先一個開始位被發送出去,同時發送數據由發送保持寄存器裝載到發送移位寄存器中,而將數據以波特率時鐘逐位發送出去,并按照線性控制寄存器的要求加上奇偶校驗位和停止位。其時鐘、幀結構配置和工作過程與接收模塊類似,因此,發送模塊也可以通過相似的狀態機實現。

2.3 中斷仲裁模塊

UART的中斷分為4個等級,其對應的中斷事件為:接收模塊線性狀態、接收數據準備就緒、發送保持寄存器空和MODEM狀態,它們記錄在中斷識別寄存器中。UART通過讀取中斷識別寄存器檢測所有的中斷信號,然后指明優先級最高的中斷給外部接口。該模塊使用狀態機實現時,共分為5個狀態,其中4個等級的中斷各為一個狀態,外加一個空閑狀態,根據每次讀取中段識別寄存器的結果確定應進入哪一狀態,從而保證了各級中斷依次被響應。

評論