一種基于FPGA的PXA270外設時序轉換接口設計

1 引言

ARCNET協議應用于高速動車組列車通信網絡時,產生中央控制單元處理器PXA270與專用協議控制器件COM20020相連的時序不匹配問題,若用通用數字電路模塊進行時序轉換,PXA270需占用PXA270專門的資源(CPU時間片)對 COM20020的寄存器、數據包緩沖區進行低速讀寫訪問(對COM20020的相鄰兩次讀操作相隔至少300 ns),這樣將增加處理器的負擔。基于這種現狀,提出一種基于FPGA的PXA270外設時序轉換接口設計方案,以FPGA為橋梁進行時序轉換,并增加存儲器直接訪問DMA(Direct Memory Aeeess)功能,即FPGA自動完成數據包的收發工作,PXA270則只需高速讀寫訪問FPGA中的同步雙口RAM。

2 時序轉換接口整體設計

2.1 FPGA對外接白

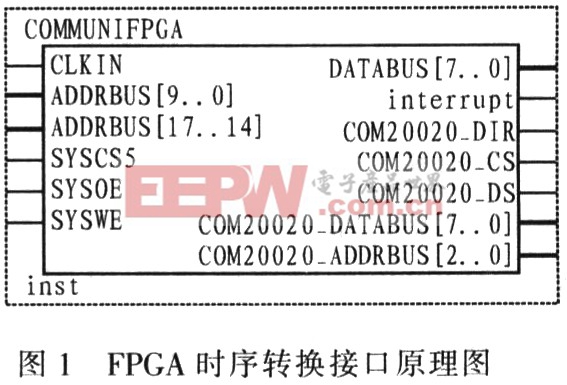

采用FPGA連接PXA270處理器與外設以解決PXA270處理器與外設直接連接時的時序不匹配問題。如圖1所示,FPGA從PXA270處理器獲得地址總線(ADDRBUS[17..14], ADDRBUS[9..0]),片選信號(SYSCS5),讀允許(SYSOE),寫允許(SYSWE),并提供雙向數據端口DATABUS[7..0] (可根據實際應用修改為32位或16位等),中斷(interrupt);同時,FPGA向COM20020提供特定的總線接口,包括 COM20020_DS,COM20020_CS,COM20020_DIR,COM20020_DATABUS [7..0],COM20020_ADDRBUS[2..0]等。

2.2 內部功能實現

PXA270和外設之間的連接是將FPGA中的雙口RAM作為數據中轉站,以此間接相連。該設計由以下4個功能模塊組成。

(1)PXA270對外設指定寄存器單次寫操作PXA270先將所要寫的數據送人雙口RAM,然后PXA270向FPGA的命令寄存器寫入對該外設指定寄存器的單次寫指令,然后FP-GA根據接收到的命令將RAM中的數據輸出到外設數據總線,同時給出對外設的寫時序。

評論