基于CPLD和Embedded System的LED點陣顯示系統的實

2 軟件設計和編寫

2.1 主控電路CPLD芯片設計與調試

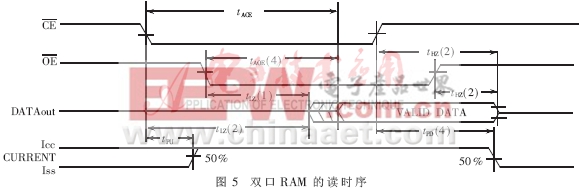

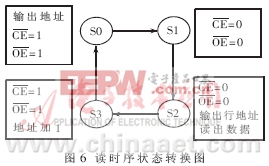

主控電路的功能是讀取雙口RAM中的數據并通過譯碼邏輯電路將數據顯示在LED點陣顯示屏的特定位置上。因為只用到單片機的一部分功能,所以使用CPLD芯片將MCU中的總線讀控制器及其外圍譯碼邏輯電路集成在一起。如若采用傳統方案,就必須采用多片芯片;而使用CPLD后,只用一片芯片就可以實現所要的功能。總線讀控制器是產生時序的電路,需根據存儲器的讀時序進行設計,只有保證正確的時序才能讀出數據。雙口RAM的讀寫時序和普通RAM的讀寫時序基本相同,如圖5所示。在片選信號從高變低之前必須輸出地址信號給雙口RAM,然后再用讀信號去控制

步驟S0 在RAM的片選CE使能之前輸出地址;

步驟S1 選中RAM,輸出讀信號;

步驟S2 行計數器輸出,讀出RAM的數據并反相輸出;

步驟S3 片選禁止,讀禁止,地址計數器加1。

評論