理解FPGA 中的壓穩態

3

為消除異步信號傳送時壓穩態導致的失敗,電路設計人員通常在目的時鐘域中使用多個串聯寄存器( 同步寄存器鏈或者同步器),將信號重新同步到新時鐘域上。采用這些寄存器,在設計中的其他部分使用壓穩態信號之前,該信號能夠有更多的時間轉換到確定狀態。同步寄存器至寄存器通路上的時序余量是壓穩態信號穩定所需要的時間,被稱為壓穩態穩定時間。

同步寄存器鏈或者同步器是滿足以下要求的寄存器序列:

■ 鏈上的寄存器都由相同的或者相位相關的時鐘進行同步

■ 鏈上的第一個寄存器由不相關的時鐘域進行驅動,即異步驅動。

■ 每個寄存器只扇出連接一個寄存器,鏈上的最后一個寄存器除外。

同步寄存器鏈的長度是滿足以上要求的同步時鐘域中的寄存器數量。圖3 是長度為2 的同步鏈的例子,假設輸出信號被送入多個目的寄存器。

圖 3. 同步寄存器鏈實例

注意,異步輸入信號,或者在不相關時鐘域之間傳輸的信號,會在相對于采集寄存器時鐘沿的任意點進行轉換。因此,設計人員無法預測數據轉換前的信號轉換順序或者目的時鐘邊沿數量。例如,如果在時鐘域之間傳送異步總線信號,并進行同步,數據信號會在不同的時鐘沿進行轉換。結果,會接收到不正確的總線數據。

設計人員必須適應這種電路工作方式,例如,雙時鐘 FIFO (DCFIFO) 邏輯存儲信號或者握手邏輯等。FIFO邏輯使用同步器在兩個時鐘域之間傳送控制信號,然后,數據被寫入雙端口存儲器,或者讀出。Altera 為這一操作提供DCFIFO 宏功能,它包括各種級別的延時,為控制信號提供亞穩態保護。如果異步信號被用作兩個時鐘域之間的部分握手邏輯,控制信號會指出數據什么時候才能在時鐘域之間進行傳輸。在這種情況下,采用同步寄存器以確保亞穩態不會影響控制信號的接收,在任何亞穩態條件下,數據都有足夠的建立時間,在使用數據之前達到穩定。在設計比較好的系統中,每一信號在被使用之前都能達到穩定狀態,設計可以正常工作。

計算亞穩態MTBF

亞穩態平均故障間隔時間MTBF 大致估算了亞穩態導致出現兩次設計失敗之間的平均時間。較大的MTBF( 例如亞穩態失敗間隔數百甚至數千年) 表明非常可靠的設計。所需要的MTBF 取決于系統應用。例如,急救醫療設備需要的MTBF 要比消費類視頻顯示設備長得多。增大亞穩態MTBF 能夠減小信號傳輸導致設備出現亞穩態問題的概率。

可以使用設計信息以及器件特征參數來計算設計中某些信號傳輸或者所有信息傳輸的亞穩態MTBF。采用下面的公式和參數來計算同步器鏈的MTBF:![]()

C1 和C2 常數取決于器件工藝和工作條件。

4

在fCLK 和fDATA 參數取決于設計規范: fCLK 是接收異步信號時鐘域的時鐘頻率, fDATA 是異步輸入數據信號的觸發頻率。較快的時鐘頻率以及觸發數據能夠降低( 或者劣化) MTBF。

tMET 參數是亞穩態信號達到確切狀態的亞穩態建立時間,即,超出寄存器tCO 的時序余量。同步鏈的 tMET 是鏈上每一寄存器輸出時序余量之和。

設計中每一同步器鏈的MTBF 確定了總的設計MTBF。同步器的失效率是1/MTBF,將每一同步器鏈的失敗概率相加得到整個設計的失敗概率,如下所示:

設計亞穩態MTBF 為1/failure_ratedesign。

設計人員使用Altera® FPGA 時,不需要手動完成這些計算,這是因為Altera Quartus® II 軟件將亞穩態參數集成到了工具中。

確定亞穩態常數

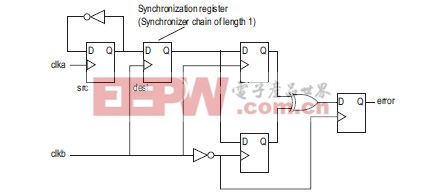

FPGA供應商可以通過FPGA的亞穩態特性來確定MTBF方程中的常數。確定特性的難點在于典型FPGA設計的MTBF 一般在幾年以上,因此,使用真實設計,在實際工作條件下測量亞穩態事件之間的時間間隔是不可行的。為確定器件亞穩態常數, Altera 使用了測試電路,設計的這一電路具有較短的可測量MTBF,如圖4 所示。

圖 4. 亞穩態特性參數測試電路結構

在這一設計中, clka 和clkb 是兩路不相關的時鐘信號。同步器輸入數據在每一時鐘周期進行觸發( 較大的fDATA)。同步器長度為1,這是因為一個同步寄存器連接了兩個目的寄存器。目的寄存器在一個時鐘周期后以及一個半時鐘周期后采集同步器輸出。如果信號在下一時鐘沿到達之前進入亞穩態,電路探測到采樣信號出現了不同,輸出一個錯誤信號。這一電路能夠探測到半時鐘周期內出現的大部分亞穩態事件。

評論