優化FPGA功耗的設計技術

無論從微觀到宏觀、從延長電池壽命到減少全球變暖的溫室效應等等,各種不同因素都在迅速推動系統設計人員關注節能問題。一項有關設計優先考慮事項的最新調查指出,大部分工程師已把功耗排在首位,或者是將其緊跟在性能、密度和成本之后。

本文引用地址:http://www.j9360.com/article/191790.htm在功耗方面,FPGA帶來了獨特的挑戰。系統設計人員只要能夠透徹充分的了解這些挑戰,以及應對挑戰所需的新技術、新方法和新工具,就能夠發揮基于FPGA的便攜式系統的部署優勢。隨著業界越來越多地采用FPGA,為更廣泛的應用產品提供靈活性并加快其上市速度,這點便顯得愈加重要。

評估某個FPGA架構是否適用于現今的功率敏感應用,必須深入研究功率方程。要做到這一點,我們可以在投入可行設計解決方案(劃分、時鐘和功率門控、電壓分軌等等)前, 對FPGA的功率特性及其影響進行分析,并使用優化工具來實現。

實現低功耗設計

根據所選FPGA技術類型的不同,電源可以看成是由靜態、動態、上電(或浪涌)、配置以及不同低功耗模式等成分組成。

靜態和動態電源是所有IC設計人員都熟知的問題。靜態電源源于以下幾種形式的泄漏電流:亞閾值泄漏、結泄漏、柵致漏極泄漏(GIDL)和柵極泄漏。動態電源則指器件工作期間的電源,與所用功能性資源(邏輯區塊、時鐘樹、嵌入式RAM、PLL等) 、I/O上的負載和阻抗終端、時鐘頻率、數據模式以及到達動態特性、信號活動或觸發率,以及信號靜態概率等因素有關。

在設計易失性SRAM FPGA解決方案時,除靜態和動態電源之外,設計人員還必須考慮到其它三種電源成分。在系統與器件功能性上電期間,浪涌電源和配置電源可能會意義重大,就如同睡眠(靜態)模式下所需的電源一般。除此之外,由于SRAM FPGA是易失性的,它們必須通過一個外部設備驅動程序(通常保存在PROM中)來啟動,這增加了系統的額外功耗和啟動延時。

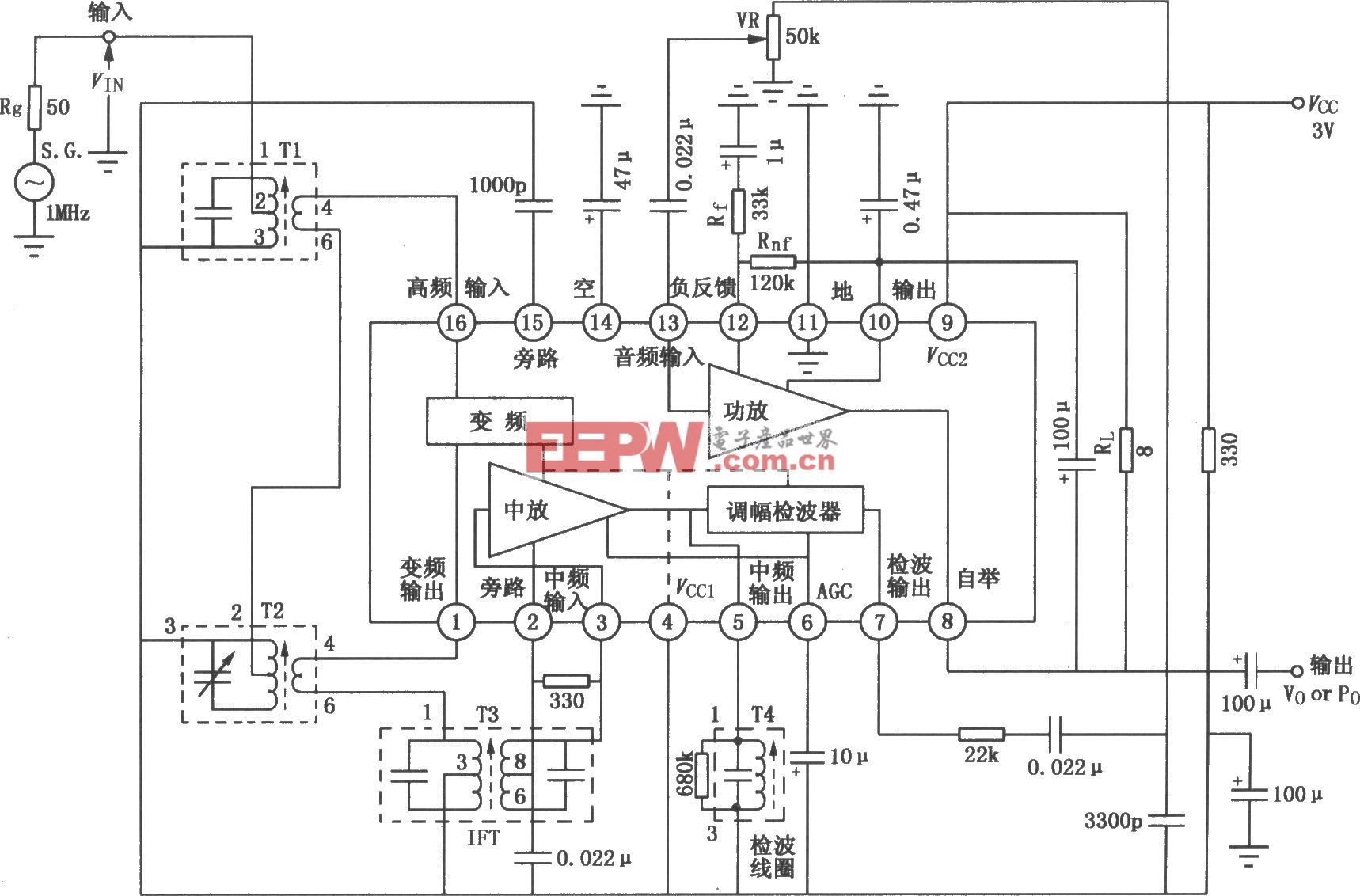

雖然SRAM FPGA供應商不斷努力降低產品功耗,但市面上的這些器件仍然耗能過高,從而極大增加了總體的系統功耗,尤其是將幾個FPGA安裝于單個電路板上,或者是不同電路板的FPGA共用一個電源時。對于需要頻繁開/關的系統,這種影響則更大,所以估算電池壽命時必須將之考慮在內。因此,在為基于SRAM的可編程器件確定電源大小或選擇電池時,系統設計人員務必要考慮到配置和浪涌電源。另一方面,真正的FLASH FPGA是非易失性的,不會產生浪涌或配置電流,而且總體靜態功耗較低,這樣一來,設計任務就比較簡單,功耗亦大大減小(圖1)。

圖1:易失性SRAM FPGA與非易失性真正 FLASH FPGA的電流曲線比較

評論