基于PC104總線和CPLD的測頻模件設計

摘要:根據某測試系統的需要,設計基于PCl04總線和CPLD的高精度測頻模件,采用多周期同步測頻法實現對所測頻段的等精度測量。設計了該測頻模件的硬件電路,并給出用CPLD實現數字頻率計的詳細VHDL源代碼。采用原理圖的方式編寫PC104總線的接口邏輯,并利用Max+P-lusⅡ軟件進行仿真。結果顯示頻率計及接口邏輯均可正確工作。實際應用表明,該測頻模件具有精度高,可靠、穩定等優點。

關鍵詞:PCl04;CPLD;多周期同步測頻;VHDL

隨著科學技術的發展,嵌入式產品在軍事領域的應用日益廣泛,特別是在各種系統的自動化測試領域。頻率測試是測試系統中的重要測試項目,在此設計一種基于PC104嵌入式計算機和CPLD的高精度測頻模件,以滿足對頻率量的測試。

1 測頻原理

傳統的頻率測量方法有兩種:直接測頻法和測周期法。直接測頻法就是在給定的閘門信號中填入被測脈沖,通過必要的計數線路,得到填充脈沖的個數,從而算出待測信號的周期。它的主要缺點是存在被測脈沖的±1個誤差,難以兼顧低頻和高頻實現等精度測量,所以測量準確度較低。測周期法是在一個信號周期內記錄下基準定時脈沖的個數,然后換算成頻率f。主要缺點是存在基準脈沖的±1個誤差,適用于較低頻率的測量。

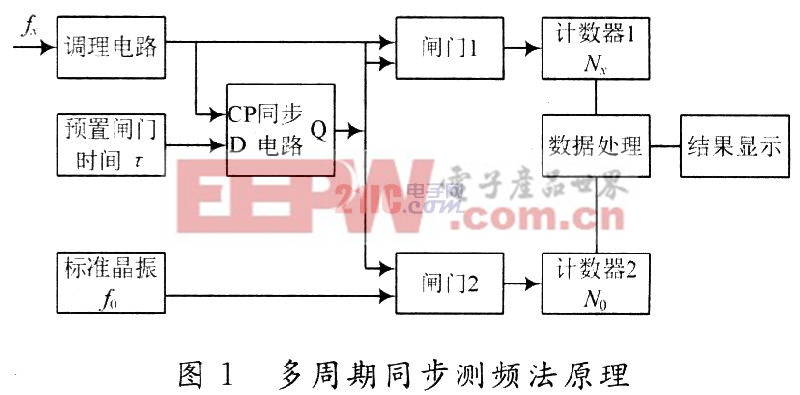

多周期同步測頻方法是在直接測頻的基礎上發展而來的,其特點在于測量過程中實際閘門時間不是固定值,而是被測信號周期的整數倍,即與被測信號是同步的,因此消除了對被測信號計數產生的±1個誤差,測量精度大大提高,而且達到了在整個測量頻段的等精度測量。多周期同步測頻法的原理,如圖1所示。

如圖1所示,首先,由控制線路給出閘門開啟信號,計數器等到被測信號的上升沿到來時,真正開始計數;然后,兩組計數器分別對被測信號和標準頻率信號計數。當控制線路給出閘門關閉信號后,計數器等到被測信號下降沿到來時結束計數,完成一次測量過程。可以看出,實際閘門與設定閘門并不嚴格相等,但最大差值不超過被測信號的一個周期。被測頻率的計算方法為:

式中:Nx為被測信號的計數值;N0為標準頻率信號的計數值;f0為標準頻率信號的頻率;τ為閘門時間,計數器的開閉與被測信號完全同步,即在實際閘門中包含整數個被測信號的周期,因而不存在對被測信號計數的±1個誤差。

2 硬件電路設計

如圖2所示,該模件硬件主要包括PC104控制處理模塊、CPLD測試模塊、信號調理模塊、繼電器驅動模塊和高精度20 MHz晶振。在該系統中為了實現對多路頻率信號的測量,采用了通過繼電器控制來選擇信號的方案。通過CPLD控制繼電器的動作,接通不同的繼電器開關,被測信號通過繼電器之后,由6N137高速光電隔離器隔離、電平轉換之后送入CPLD進行測頻。由于CPLD的I/O口驅動電流較小,所以加了一級ULN2803驅動器來驅動繼電器的線包。CPLD主要完成的功能是實現數字頻率計,采用多周期同步測頻法完成對輸入信號頻率的測量,并通過與PC104的接口邏輯,將測量結果送給PC104主機,由主機進行頻率值的計算及顯示,從而完成整個測頻模件的功能,CPLD選用Altera公司的EPM7128SQCl00芯片。

3 軟件設計

3.1測頻電路程序設計

對于CPLD的編程,一般有通過電路原理圖的方式和通過硬件描述語言即VHDL語言兩種方式。第一種方式直觀性強,較好理解,適用于小規模數字電路的設計;第二種方式具有多層次描述系統硬件功能的能力,可讀性強,適用于時序電路及大規模電路的設計。本文采用兩者相結合的方式,用VHDL語言實現數字頻率計的設計,用原理圖的方式實現了PC104主機的接口邏輯,并進行仿真。結果表明完全可以滿足功能需求,編譯環境為Max+PlusⅡ。

以下為數字頻率計的VHDL語言源代碼。設計了兩個32位計數器,一個8位數據選擇器及一個觸發器控制閘門信號。

以上程序通過軟件編譯后生成數字頻率計的邏輯功能模塊圖如圖3所示。以下是程序的仿真波形(見圖4),標準頻率為20 MHz,被測信號頻率為O.1 MHz,仿真時間設為120μs。

從仿真的結果可以看出,在定時脈沖CL到來時,計數器并沒有開始計數,而是等到被測信號的上升沿到來時,START信號才開啟,計數器開始計數,定時脈沖結束時,計數器也是等到被測信號的上升沿到來時才結束計數,實現了多周期同步測頻。圖4中被測信號頻率的計算方法如式(1)所示。與系統預設值相同,可以實現所需的功能。

3.2 PC104接口電路實現

該設計中PC104接口電路部分在Max+PlusⅡ中用原理圖的方式實現。使用的PC104總線信號有地址線A0~A9、數據線D0~D7、讀寫信號線IOR/IOW、復位信號RESET、中斷信號IRQ3、地址允許線AEN。在PC104總線的接口電路部分遵循一個原則:就是輸出加鎖存,輸入加緩沖驅動。該接口電路示意如圖5所示,首先地址線的A3~A9位與外部波段開關設置地址及AEN信號通過譯碼電路中的比較器進行比較,若相同,則說明該模塊被選中,然后根據A0~A2的譯碼結果,結合讀寫信號線產生輸出鎖存器74HC273及輸入緩沖器74HC244的脈沖信號或使能信號,完成對數字頻率計及外部電路的讀寫及控制。在總線工作方式上采用中斷方式。設計中,將計數器的實際計數結束信號EEND作為總線的中斷觸發信號IRQ3,以此來提高PC104總線的工作效率。該接口邏輯的仿真結果如圖6所示。

從仿真結果可以看出,接口邏輯可以很好地控制外部繼電器的接通,產生清零及定時脈沖,并能正確地讀取數字頻率計的計數結果,實現模塊預定的功能。該接口邏輯已在實驗中得到了驗證。

3.3 PC104應用程序設計

在調試該模件時系統采用Windows。Me操作系統,編譯環境采用TC 3.0。主程序包括系統初始化、中斷初始化、接通繼電器及產生清零和定時脈沖模塊。在中斷服務程序中主要完成了讀取計數值、計算頻率值及顯示打印功能。它的程序流程圖如圖7所示,在此不再列出具體代碼列。

4 實驗結果

實驗采用的方法是將板載的20 MHz的晶振在CPLD內部分別進行2分頻和20分頻,得到10 MHz和1 MHz的信號,然后再將這兩個頻率信號分別進行2.4,6,8分頻,得到共9個被測信號,閘門時間為1 s,測試結果如表1所示。

由測試結果可以看出,模件的測頻精度較高,完全能夠滿足一般性測試系統的需要。

5 結語

采用多周期同步測頻技術設計并實現了基于PC104總線和CPLD的測頻模件。給出硬件設計原理圖和數字頻率計的VHDL程序源代碼,PC104總線的接口邏輯電路,最后得出仿真結果,編制了PCl04總線應用程序。實際應用表明,該模件精度高,穩定性好,能夠很好地完成對頻率量測試的任務。

評論