復用器重構降低FPGA成本

關鍵詞: FPGA;復用器;重構;重新編碼;總線;邏輯優化;綜合

1. 引言

--- 復用器是數據通道常用的構建模塊,被廣泛應用在處理器[1]、處理器總線、網絡交換,甚至是資源共享的DSP設計中。據估計,復用器一般要占用一個FPGA設計[2] 25%以上的面積。因此,優化FPGA設計的關鍵在于怎樣優化復用器。

--- 本文介紹了一種新的復用器重構算法,該算法減小了復用器在基于4輸入查找表(4-LUT)FPGA體系結構中所占用的面積。基準測試結果表明復用器平均減少了17%,在一些設計中,4-LUT整體減少20%。

--- 2.1節闡述了復用器是如何由行為級VHDL[4]或Verilog[5]代碼產生的,2.2和2.3節闡述復用器樹和復用器總線在設計中是怎樣生成的。2.4節說明這些結構怎樣由4-LUT實現,闡述如何采用兩個4-LUT有效實現一個4:1二進制復用器。

--- 第3節介紹了一種叫做壓縮的新技術,該技術附加一些控制邏輯,將多個2:1復用器重新組合為有效的4:1復用器,從而減少了為總線上每一個比特位實現復用器所需要的4-LUT數量,所附加的控制邏輯代價由整個總線來分擔。優化復用器總線是復用器重構算法的核心。

--- 4.1節闡述復用器重構算法如何構建設計中的復用器樹總線。4.2節的重構方法用于執行4.3節中定義的均衡算法。均衡增加了由壓縮生成的有效4:1復用器的數量。

--- 第5節總結了在Altera Quartus II集成綜合中運行的整個算法。第6節列出了來自120個Altera真實用戶設計實例的基準測試結果,測試表明面積減少超過20%,平均節省了4.2%。

2. 背景知識

--- 2.1 復用器在設計中是怎樣實現的

--- 行為級HDL設計中的任何條件代碼通常會綜合為復用器。本節闡述兩個最常用的復用器生成代碼實例。

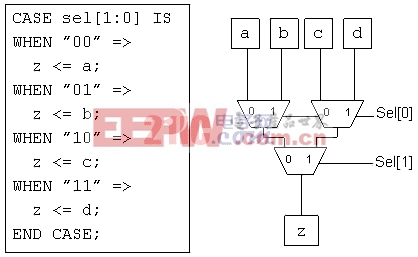

--- 圖1是VHDL的case聲明及其2:1復用器樹的實現。采用Verilog case聲明的“parallel case”指令[5]可產生相似的結果。

圖1

--- 注意,并不是所有的case聲明都能將可能的事件描述清楚,需要依靠“default”或者“others”條件來進一步說明。在這些情況下,可以繼續將case聲明表征為2:1復用器樹,但是這種樹結構可能達不到平衡。

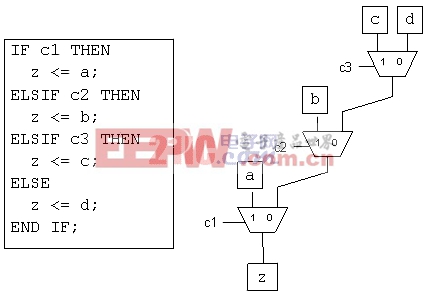

--- 圖2顯示了“if-then-else”聲明是怎樣產生一個2:1復用器鏈的。Verilog的“?:”和非平行cases可同樣產生相似的結構。注意,復用器鏈確保如果第一個if條件為“真”,將選擇“a”數據輸入,而復用器其他部分將被忽略。

--- 本文闡述的復用器重構算法應用于2:1復用器。綜合工具由行為級代碼開始通常會生成較大的復用器。較大的復用器總是被分解為2:1復用器樹,如何實現這種分解已經超出本文討論范圍。

圖2 if-then-else聲明生成的邏輯

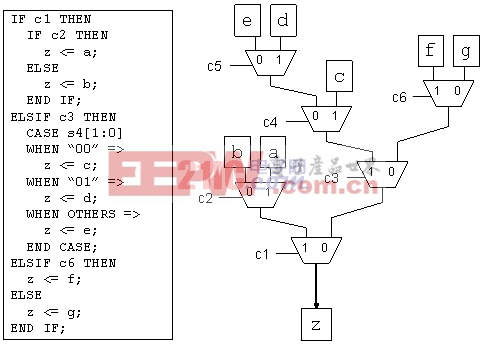

圖3 HDL生成的復用器材

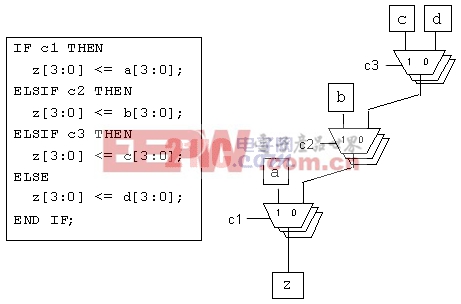

圖4 生成復用器總線

評論