高速突發模式誤碼測試儀的FPGA實現方案

摘要:突發模式誤碼測試儀與一般連續誤碼測試儀不同,其接收端在誤碼比對前要實現在十幾位內,對具有相位跳變特點的信號進行時鐘提取和數據恢復,并且在誤碼比對時須濾除前導碼和定界符,僅對有效數據進行誤碼統計。本文提出一種基于FPGA實現的高速突發模式誤碼測試儀設計方案,并介紹該方案的總體設計過程,以及FPGA中主要功能邏輯模塊的工作原理和控制系統的設計。該測試儀應用于1.25 GHz GPON系統突發式光接收模塊的誤碼測試中,具有較好的性能和實際意義。

關鍵詞:突發模式;誤碼測試儀;時鐘相位對齊;高速串行收發器

引言

無源光網絡PON以其獨特的優勢在網絡中已經規模化地應用。由于GPON系統在現有PON系統中帶寬利用率最高,系統成本最低,且具有全業務支持能力,因此其前景被普遍看好,成為眾多電信運營商和設備制造商推崇的寬帶接入技術。

在GPON中,下行數據是以廣播形式發送的,上行數據由多個用戶終端按時分多址的方式發送的數據包組成。因傳輸路徑不同,各數據包有不同衰減,不同數據包相位間存在跳變,數據包中存在長連“1”、“0”,這些因素的影響使得OLT突發接收模塊接收的信號是特殊的突發光信號。對于上行的突發信號,OLT突發接收模塊不僅要從中恢復出幅值相等的信號,而且要消除相位突變,即完成時鐘和相位的對齊,因此OLT輸出的信號應該為幅值相等且時鐘和相位對齊的電信號。本突發模式誤碼測試儀的作用是,準確地判斷被測的OLT突發接收模塊的完成幅值恢復響應時間和其可靠性。

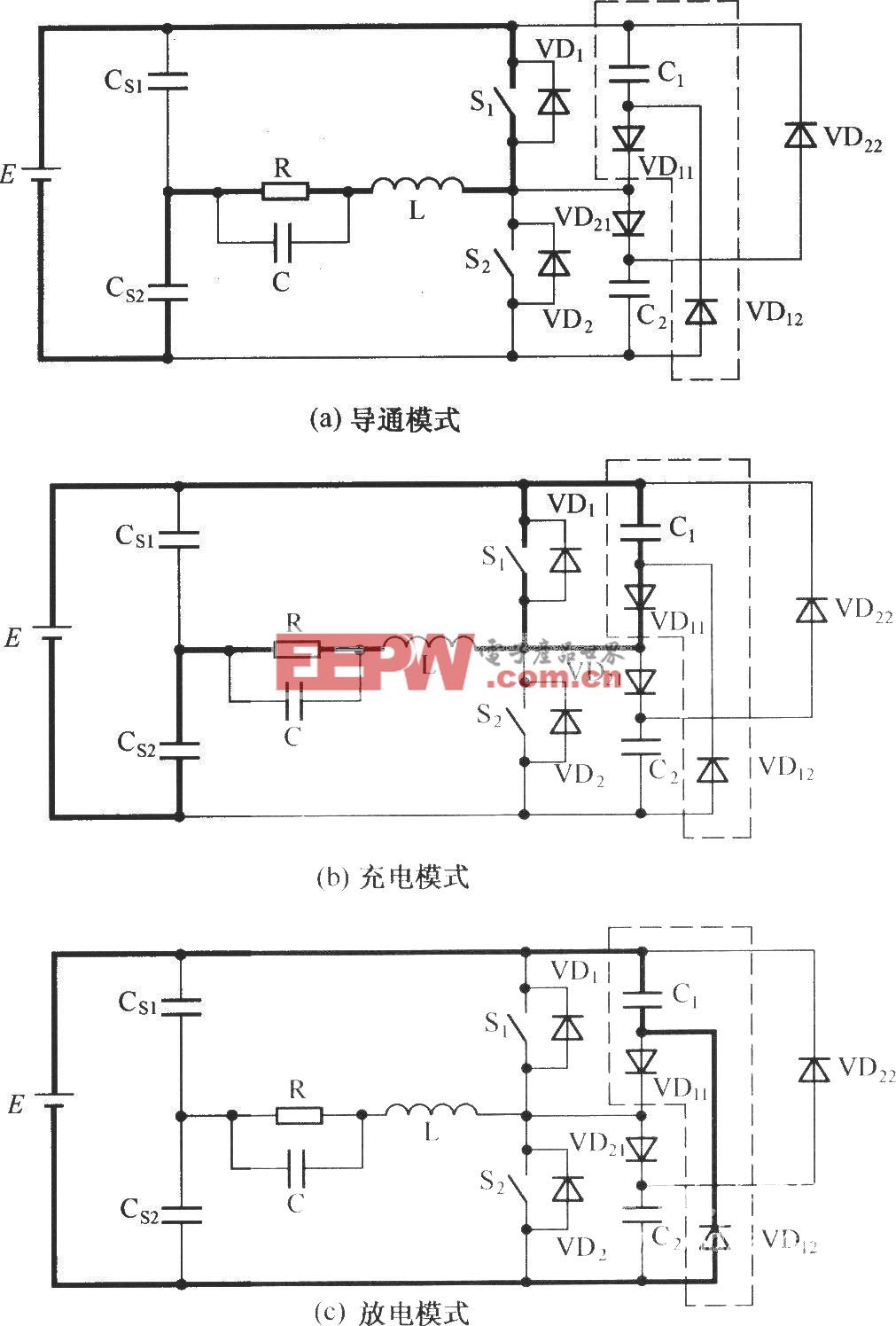

1 突發模式誤碼測試原理

與一般連續誤碼測試儀相同的是,突發誤碼測試儀也由發送和接收兩部分組成。發送部分發送可預知的信號作為測試信號來模擬實際信道中傳輸信號,并將該信號送到待測設備中;接收部分產生與發送部分相同的信號,用以和接收的信號逐位比對,并統計誤碼數和誤碼率。

與一般連續誤碼測試儀不同的是,突發誤碼測試儀發送部分發送的測試信號要模擬突發信號,即具有相位突變和幅度不均衡的特點。此外,接收部分要從接收到的可能存在相位跳變信號中準確地提取時鐘和恢復數據。

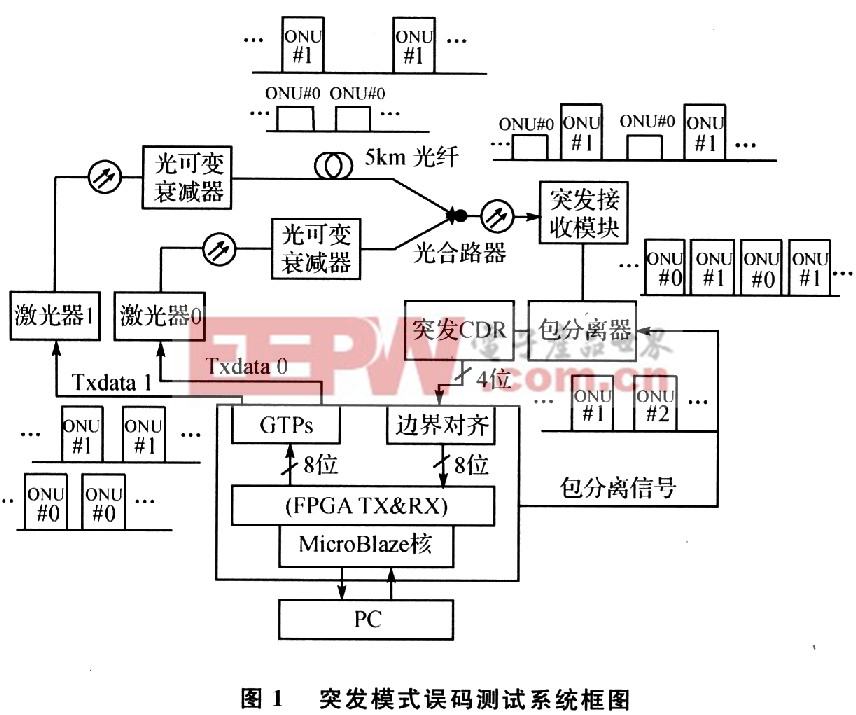

根據突發誤碼測試儀的特點,其總體設計框圖如圖1所示。

突發接收模塊(BMRx)是要測試的模塊。突發誤碼測試儀用FPGA邏輯來實現兩路時分復用(TDMA)數據的輸出,兩路數據先分別通過光可變衰減器不同幅度的衰減后,再經過不同長度的光纖的時延,最后經過光合路器合為1路信號輸出。光合路器的輸出數據近乎于實際GPON中的上行突發信號,且假定信號在經過這些路徑后沒有出現誤碼。模擬的突發信號在經過待測突發接收模塊后,經過包分離電路提取1路包數據(ON-U#1或ONU#2),該路包數據最后經過突發模式時鐘數據恢復芯片提取出時鐘和4路并行數據。FPGA將提取的時鐘作為誤碼比對的源時鐘,并將4路并行數據重構造后與本地產生的數據進行比對,統計誤碼。

評論