基于FPGA的三相函數信號發生器設計

摘要:基于FPGA的三相函數信號發生器以DDS為核心,在Altera公司CycloneⅡ系列EP2C8T144C8上實現正弦波、方波、三角波和鋸齒波信號的產生,利用單片機PICl8F4550控制波形的頻率及相位差。同時單片機通過DAC0832控制波形數據轉換DAC902參考電壓實現在波形幅度的控制,D/A輸出的波形經過放大、濾波后輸出。波形參數的輸入輸出通過觸摸屏和液晶屏實現,測試結果顯示該系統具有較高的精度和穩定性。

關鍵詞:FPGA;三相;信號發生器;DAC902

模擬函數信號發生器輸出波形易受輸入波形的影響,難以實現移相控制,移相角度隨所接負載和時間等因素的影響而產生漂移,頻率、幅度的調節均依賴電位器實現,因此精度難以保證,也很難達到滿意的效果。基于FPGA的數字式三相信號發生器,精度較高,移相控制方便,實現頻率為1 Hz~10 MHz、幅度0.1~10 V,分辨率為1°,頻率和幅度的調節均可程控的三相函數信號發生器。系統還具有輸出靈活、易于系統升級等優點。

1 函數信號發生器的原理

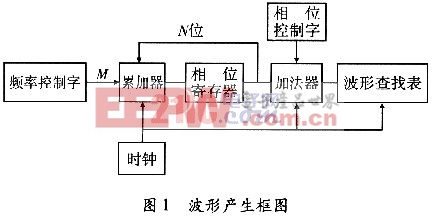

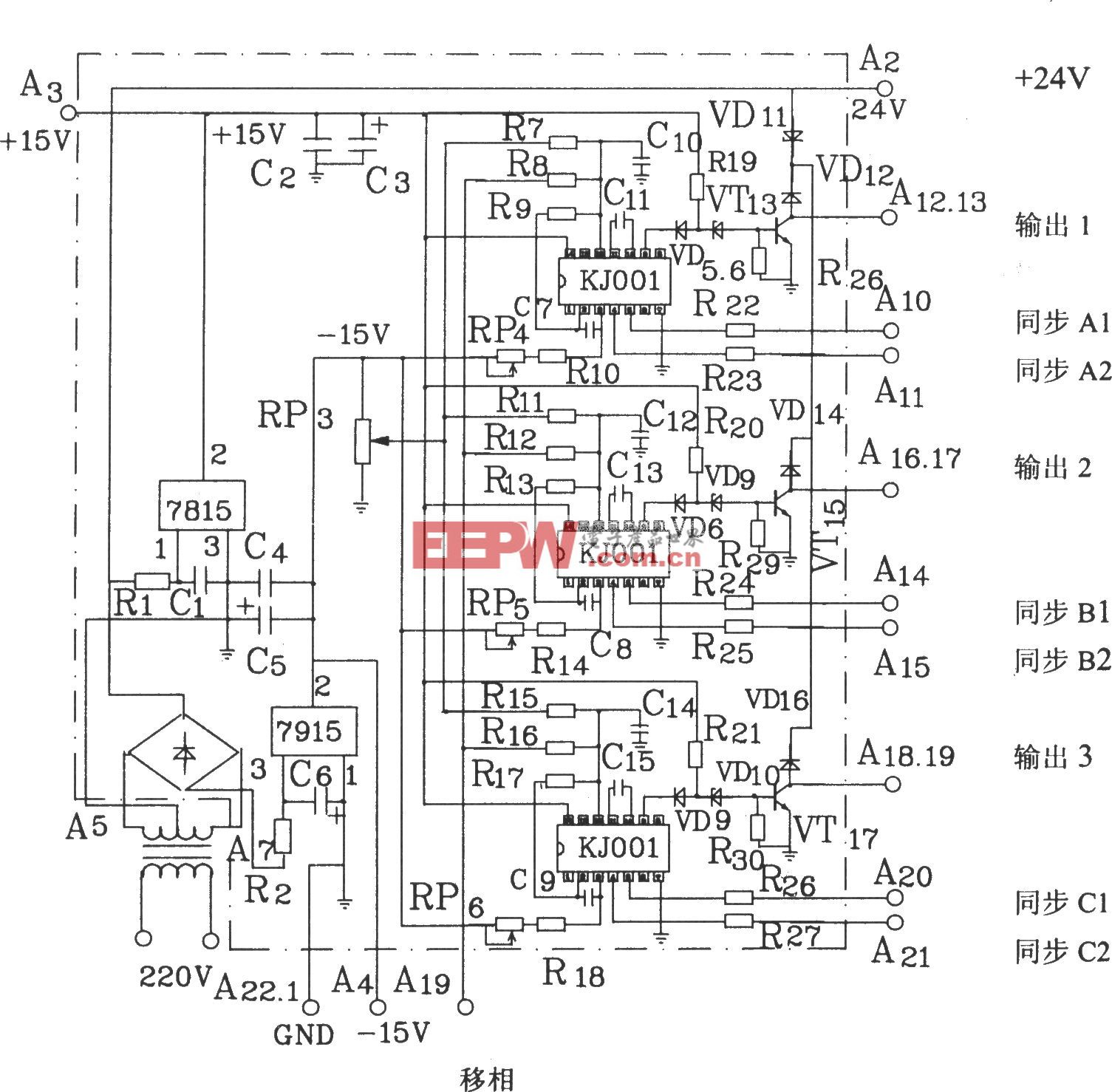

基于DDS原理,頻率控制字M和相位控制字P分別控制DDS輸出波形的頻率和相位。相位累加器是整個波形產生的核心,它有一個累加器和一個N位相位寄存器組成。每來一個時鐘脈沖,相位寄存器以步長M增加,如圖1所示。相位寄存器的輸出與相位控制字相加,其結果作為波形查找表的地址。波形查找表由ROM構成,內部存有一個完整周期的波形的數字幅度信息,每個查找的地址對應波形中0°~360°范圍的一個相位點。查找表輸入的地址信息映射達成波形幅度信號,同時輸出到數模轉換器的輸入段,DAC輸出的模擬信號經過程控濾波器,可得到一個頻譜純凈的波形。

相位寄存器每經過2N/M個fc時鐘周期后回到初始裝狀態,相應地波形查表經過一個循環回到初始位置,DDS輸出一個波形。輸出的波形周期為Tout=(2N/M)Tc,頻率為![]()

DDS的最小分辨率為fmin=fc/2N,當M=2N-l(即一個周期內只取兩個點)時,DDS最高的基波合成頻率為foutmax=fc/2,根據取樣定理,這在理論上是可行的,考慮到失真度的問題,取i(i>2)個點,則最高頻率為當M=2N-3時,foutmax=fc/i。

2 系統總體設計

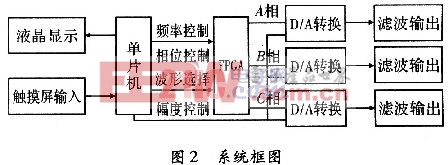

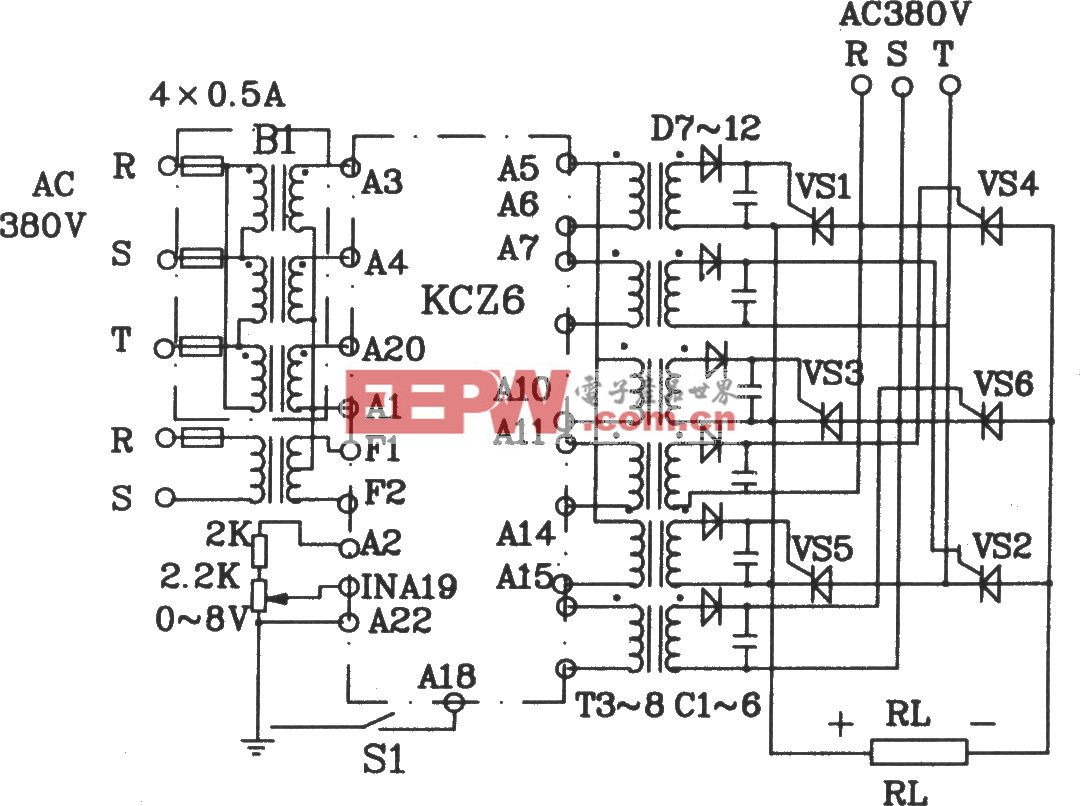

系統由單片機控制模塊、FPGA波形產生模塊、數模轉換模塊、濾波輸出模塊、觸摸屏輸入和液晶顯示模塊組成,單片機控制FPGA產生輸入頻率和相位差的三相正弦波、方波、三角波和鋸齒波,經過D/A轉換后濾波輸出,三相波形的幅度也由單片機通過改變D/A的參考電壓控制。具體系統框圖,如圖2所示。

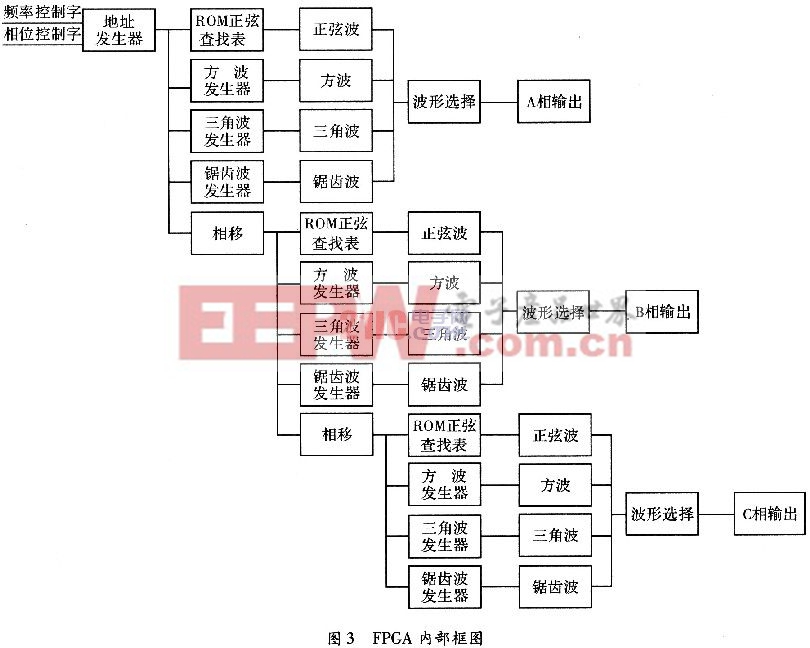

FPGA部分具體框圖,如圖3所示,基于DDS原理,主要由相位累加器、正弦波ROM查找表、方波發生器、三角波發生器、鋸齒波發生器和波形選擇模塊組成。根據單片機設置相移值調整三相波形的相位差,波形選擇也由單片機控制。

評論