基于FPGA的MC-CDMA基帶系統的實現

1 MC-COMA調制解調的硬件實現

1.1 方案設計

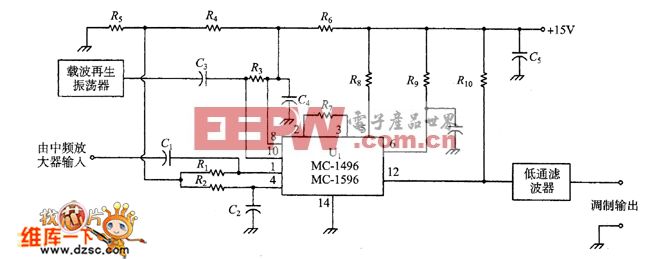

根據MC-CDMA調制解調的基本原理,在本方案設計中將其調制過程劃分為符號復制、頻域擴頻、載波調制三個功能模塊,解調過程劃分為載波解調、解擴和頻域合并三個功能模塊。考慮到代碼的整齊和運算速度的要求,在設計中采用了流水線操作方式。

根據需求,本文設計方案的子載波數為32,擴頻碼由長度為32的OVSF碼發生器產生,通過設置OVSF碼發生器的參數,可以選擇32種不同的碼字中的一種進行擴頻來區分不同用戶的數據。各個模塊之間的時序關系通過ens等控制信號實現,前端模塊運算完成才觸發后端模塊,從而實現流水線操作。

MC-CDMA調制所有程序模塊之間的關系和信號流程。其中MC-CDMA模塊為頂層模塊,第二行的三個函數為一級子模塊,第三行的函數為二級模塊。進入MC-CDMA調制器的數據符號首先經過N次復制,本文系統中N=32,Copy32子程序模塊即用于實現多載波調制中的符號復制功能。復制之后的數據送入頻域擴頻模塊sPreading,經由長度為32的OVsF碼序列進行擴頻處理后送入IFFT32運算模塊實現頻域到時域的變換,完成MC-CDMA調制。

1.2 頻域擴頻的實現

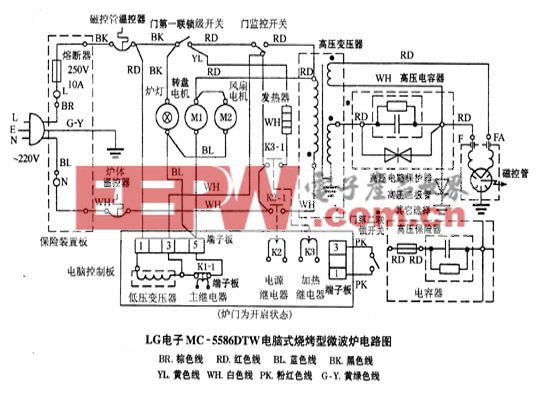

在擴頻通信系統中,其原理都是使用擴頻序列來擴展用戶的原始信號。在接收端,為了恢復原始信號,使用與發射端一樣的同步擴頻序列與收到的信號進行相關。MC-CDMA就是利用擴頻序列的互相關性進行多用戶通信的,擴頻序列在MC-CDMA系統中起著重要的作用。

1.3 FFT/IFFT的FPGA實現

本文中FFT/IFFT設計參考Altera公司FFTIP核的數據手冊[2],通過對IP核進行實際測試可知,有效數據要延遲于START信號4個時鐘周期輸入。而在本系統中,來自前端模塊的控制信號和有效數據是同步輸入FFT/IFFT變換模塊的,所以需要對輸入數據寄存4個周期。輸入數據緩沖模塊用來對輸入數據進行寄存。時序控制單元用于保證模塊中的時序對齊。FFT/IFFT運算單元是基于Altera公司的Altera Megacore IP核實現的。FFT/IFFT IP核的各個主要參數設置如表1所示。變換長度為32,采用并行流水線FO結構,為了節省slices資源的消耗,最大限度地選擇使用片內的塊RAM資源。表1給出了綜合得到的FFTIFFT模塊的資源消耗情況,從綜合報告中可知,其最大執行速度可以達到268 MHz。

2 系統綜述

2.1 系統驗證方案

基于以上所提出的2發3收MIMOMC-CDMA基帶系統發射機和接收機的設計方法,分別實現發射機和接收機的RTL代碼編寫工作并進行功能驗證之后,將發射機與接收機進行了聯合凋試,驗證了本文設計實現的2發3收MIMOMC-CDMA基帶系統的基本功能。

2發3收MIMO系統的信道處理過程類似于硬件仿真MIMO信道模塊,來自發射機2個發射端的信號xl,x2與信道矩陣相作用之后加入高斯白噪聲,得到3個數據:r1、r2、r3,送往接收機的3個接收天線端。接收機檢測算法是在假設2發3收MIMO信道矩陣的6個參數h11~h33己經被正確估計出來的基礎上進行的。系統聯合調試中的信道參數來自32個子載波的2發3收MIMOMC-CDMA的MATLAB仿真系統,首先得到仿真信道在每個載波上的參數,此時的信道參數為復數浮點數據;之后在MATLAB環境中編寫一個將任意復數轉化為可設定點結構與位寬的十六進制數據的程序,將這些復數信道參數轉化為Verilog編碼能夠識別的十六進制數,本文實現中將這些信道參數轉化為位寬為16的十六進制數,其中實部、虛部分別以高8位和低8位表示。在這8位中,1位為符號位,另外7位為預設的信道參數的值,其中2位為整數位,5位為小數位。

cdma相關文章:cdma原理

評論