基于CPLD的模數轉換組合研究

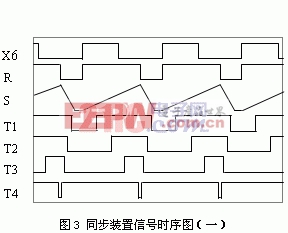

模塊1的輸入為X5、X6和來自模塊3的四個脈沖T1、T2、T3、T4,雖然X5、X6都輸入模塊1,但是只有X6與此閉環有關,它們在模塊1內經過 一系列邏輯單元處理,輸出為一系列脈沖,包括詢問脈沖X(X=1,2,3,4)、寄存器詢問脈沖、選擇脈沖、輸出自動微調脈沖和其它脈沖。模塊2的輸入R 是矩形波信號,輸出S類似于三角波。模塊3的主體是四個電位器和四個電壓比較器。四個電位器經過精心調節在滑動端形成四個等間隔的基準電壓。四個電壓比較 器將S和這些基準電壓分別進行比較,得到四個TTL電平脈沖信號T1、T2、T3、T4。T1、T2、T3、T4和S、R、X6時序關系如圖3所示。

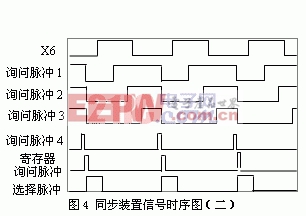

輸出脈沖與X6的時序關系如圖4所示。

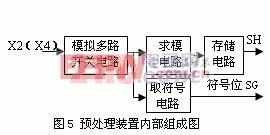

(2)預處理裝置

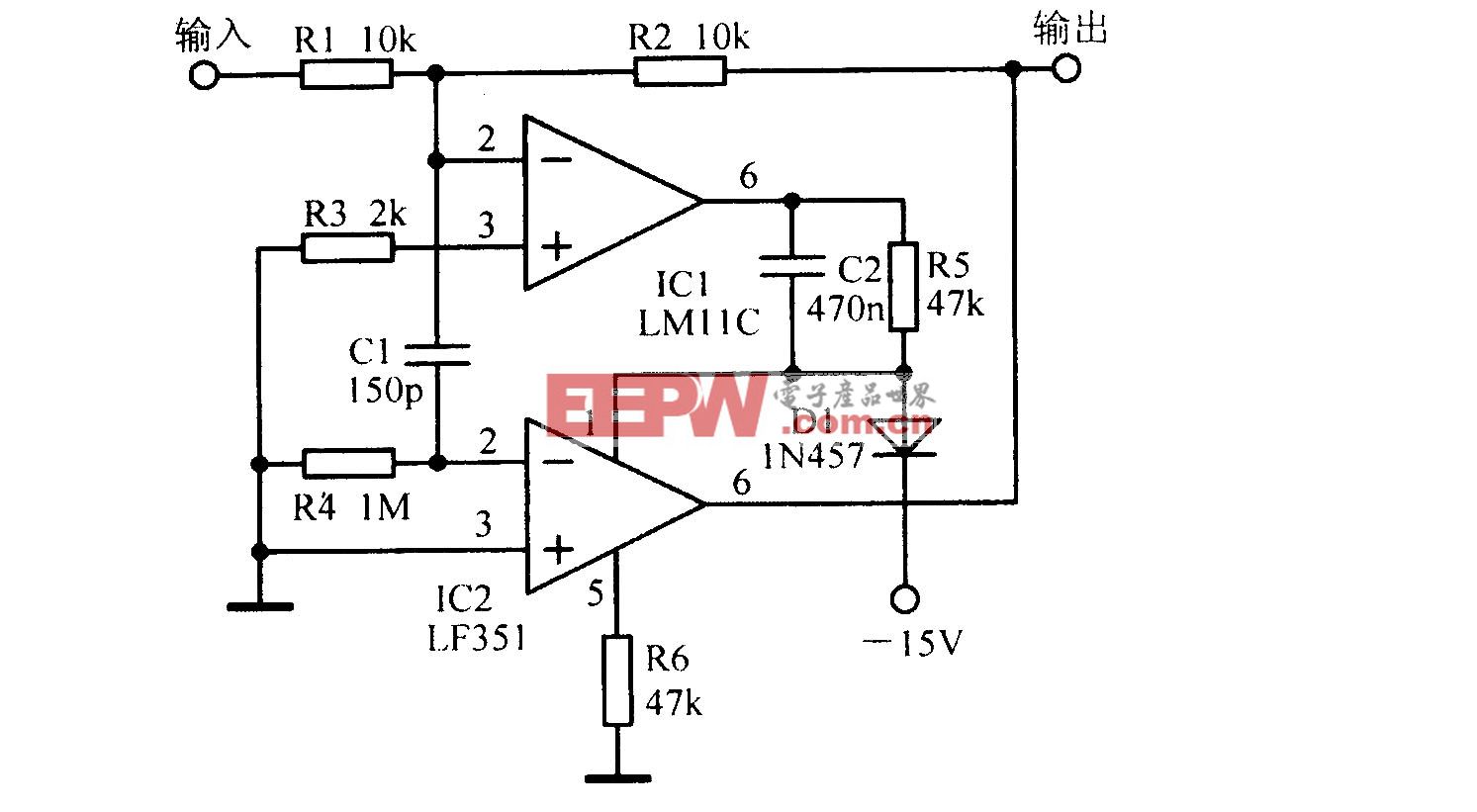

預處理裝置包括模擬多路開關電路、求模電路、取符號電路和存儲電路,其組成如圖5所示。

X2(或X4)是雙極性信號,在被模擬多路開關電路選通后,通過求模電路變為正極性信號,此正極性信號進入存儲電路進行跟蹤/保持。另外,模擬多路開關電路的輸出信號還進入取符號電路,得到符號位。

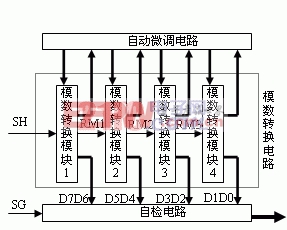

(3)模數轉換和微調自檢裝置

該裝置包括模數轉換電路、自動微調電路和自檢電路,其中模數轉換電路又由四個模數轉換模塊組成,如圖6所示。

圖6 模數轉換和微調自檢裝置內部結構圖

SH進入模數轉換模塊1,在其內部被電阻網絡分壓,分壓結果與內部基準電壓進行比較,比較結果被編碼,得到模數轉換結果的最高兩位D7D6;設數字輸出 D7×27+D6×26對應的模擬信號幅度為U1,在模數轉換模塊1內部,將SH和U1相減,輸出RM1=SH-U1,RM1進入模數轉換模塊2,按同樣 的方式得到D5D4;模數轉換模塊3、模數轉換模塊4也完全類似,分別輸出D3D2(第3位和第2位)和D1D0(第1位和第0位)。這樣就得到了模數轉 換結果的8個數據位。

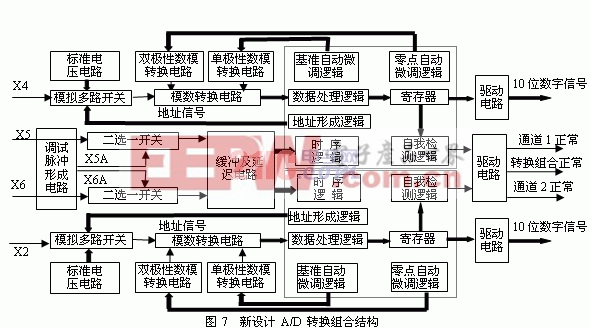

3 A/D轉換組合設計實現

新A/D轉換組合的幾何尺寸應與引進A/D轉換組合吻合,輸入輸出接口特性應與引進A/D轉換組合完全一致。鑒于原A/D轉換組合采用分立元件和低集成度芯片設計,導致電路復雜,故障率高的缺點,本文采用高集成度的CPLD芯片設計國產A/D轉換組合。

3.1總體功能設計

新A/D轉換組合總體設計框圖如圖7所示,當X5(自動微調脈沖)為低電平時,地址形成邏輯形成的地址信號使模擬多路開關選通來自前端接收系統的模擬輸 入信號X2(或X4)。X2(或X4)經過模擬多路開關送入模數轉換電路進行轉換。模數轉換電路輸出的數字信號經數據處理邏輯變換后,得到與原模數轉換組 合碼制相同的10位輸出信號,即8位數據位、1位符號位和1位奇校驗位。這10位信號經寄存器鎖存后,通過驅動電路送至后端計算系統。

評論