基于FPGA和TMS320DM642的CCD圖像采集和處理系統硬

當CCD產生的視頻信號為模擬信號對,對其直接傳輸、存儲和處理比較困難,須要將模擬視頻信號轉換為數字視頻信號,以便對其進行處理,并進行高效可靠的傳輸和存儲。當前,數字圖像采集和處理系統不僅要面臨高速寬帶、高精度的挑戰,而且對采樣時機、采樣點數、采樣速率的可控性也提出了較高的要求,本文提出了一種實時圖像采集和處理系統的設計方法,該系統以TMS320DM642[1-2]為核心,結合視頻解碼芯片SAA7115H和OSD FPGA構成實時圖像采集和處理系統電路。

1 系統總體設計

1.1 系統結構

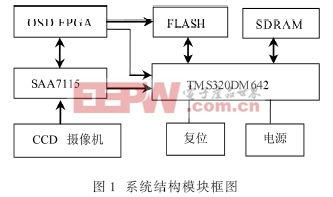

本系統以TMS320DM642為核心,采用模塊化設計思想,整個系統主要由視頻解碼芯片(A/D轉換芯片)、可編程邏輯門陣列(OSD FPGA)、TMS320DM642及外圍電路組成。外圍電路主要包括CCD攝像機、SDRAM圖像存儲器、FLASH程序存儲器及TMS320DM642外圍電路(復位、電源連接等)。圖1為該系統的結構框圖。

1.2 系統工作原理

由CCD攝像頭攝入的PAL制圖像傳送到SAA7115解碼器,SAA7115解碼器將信號轉變成并行的BT.656圖像碼流送至TMS320DM642視頻口VP0,TMS320DM642將其再解碼,得到YUV(4:2:2)格式的圖像,并通過EDMA傳輸到動態存貯器(SDRAM)中存儲,圖像大小為每場720×288(寬×高),每幀720×576(寬×高)。CPU通過訪問SDRAM中的圖像數據,依照相應的程序進行相應的圖像處理。

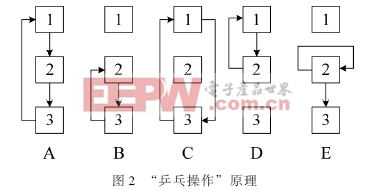

在實時圖像處理系統中,為了不影響數據處理速度,需要在恒速的CCD圖像采集與變速的TMS320DM642圖像處理之間加入緩沖電路,緩沖采用TMS320DM642視頻口的片內FIFO和片外SDRAM的乒乓緩存結構。“乒乓操作”是一個經常應用于數據流控制的處理方法,如圖2所示,其處理流程為:輸入數據流通過指針等時地將數據流分配到數據緩沖區1、2和3中,在第1幀的時間,將輸入的數據流緩存到1;第2幀將輸入的數據流緩存到2,與此同時,將1的數據作運算處理。在下個緩沖周期,再次切換,將輸入的數據流緩存到3,與此同時,將2的數據運算處理。如此循環,A、B、C、D、E為其5種狀態。

乒乓操作的最大特點是按節拍、相互配合地切換,將經過緩沖的數據流不停頓地進行運算及處理。把乒乓操作模塊當作一個整體,此模塊兩端的輸入數據流與輸出數據流均是連續不斷的,沒有任何停頓,因此非常適合進行流水線式處理,完成數據的無縫緩沖與處理。

2 功能模塊設計

2.1 視頻采集模塊

本系統采用Philips公司的SAA7115視頻解碼芯片將CCD模擬視頻進行數字化,然后傳給TMS320DM642的視頻端口進行處理,同時分離水平同步(XRH)和垂直同步(XRV)等信號。

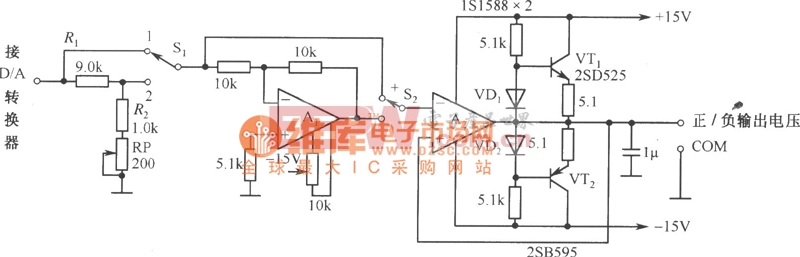

視頻解碼芯片采用SAA7115,省去時鐘同步電路的設計,簡化接口電路,提高系統的可靠性。由攝像機采集到的模擬信號經過視頻端子進入到解碼器SAA7115的模擬端Al11,經模擬處理和A/D轉換后產生數字色度信號和亮度信號,分別對其進行處理。亮度信號處理的結果一路送到信號處理器,進行綜合處理,產生Y和UV信號,經格式化后采用4:2:2 YUV格式從IPD[7-0]輸出直接連接到TMS320DM642視頻口的VP0[9-2]管腳;另一路經過同步分離器,由數字PLL產生相應的同步信號與TMS320DM642的VP0CTL0和VP0CTL1相連,同時PLL驅動時鐘發生器,產生27 MHz的時鐘同步信號LLC,輸出到TMS320DM642的VP0CLK0管腳。解碼器SAA7115與TMS320DM642的視頻接口的原理如圖3所示。

評論