基于FPGA的多功能密碼鎖的設計

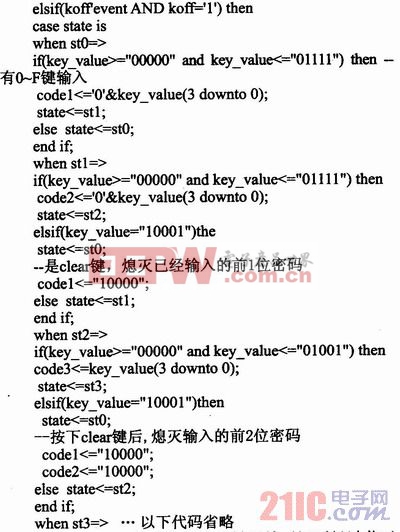

實現圖2流程的部分關鍵代碼如下:

本文引用地址:http://www.j9360.com/article/191204.htm

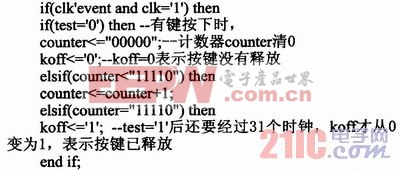

本文引用地址:http://www.j9360.com/article/191204.htm 完成消除抖動的進程是在按鍵釋放后還要經過若干個時鐘的延遲再判斷按鍵是否釋放,若真的釋放,信號koff才從0變為1,該信號也是控制模塊根據密碼輸入進行狀態轉移的觸發信號。例如按下鍵產生的前沿抖動,這個抖動產生的假釋放高電壓一般不會持續太多個時鐘(若系統的時鐘頻率高可以增加代碼中計數器的位寬以增加延時),之后又變為穩定的低電平,則該進程再一次對計數器進行清零,重新判斷。

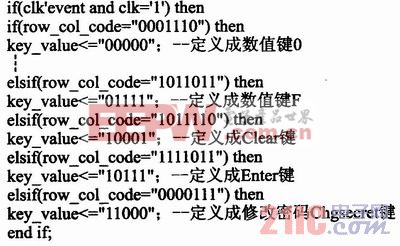

鍵值編碼功能是將按下鍵的行列位置碼賦予相應的鍵值,自然地將0~F鍵定義成鍵值為0~15,功能鍵的定義比較隨意。實現的部分代碼如下:

評論