基于FPGA的電臺接口轉換模塊設計

摘要:目前市場上電臺接口轉換模塊大多都采用模擬電路,其帶來穩定性差,工藝復雜等缺陷。通過采用數字信號處理技術來處理信號通信,提高信號的傳輸速率和降低傳輸的誤碼率,并提高系統的穩定性,節省信道資源。這里采用FPGA作為核心芯片來設計和開發,利用DSP Builder來仿真FFT實驗,用OuartusⅡ軟件開發設計此接口轉換模塊,最終獲得的模塊電路系統穩定,PTT信號更純凈。

關鍵詞:FFT;FIR;Cordic算法;穩定處理

一般來說,無線電臺通信采用半雙工通信方式,一方在發送話音信號的同時,不能接收另一方的話音信號。因此電臺的通信接口分為兩部分,一部分為話音信號接口,用于發送接收話音,另一部分為PTT控制信號接口,用于控制電臺的發送接收狀態。然而,目前有許多通信設備,如民航、海事、鐵路交通的內部通信以及應急通信等,為了實現電臺的遠程遙控,并且節省信道資源,將PTT控制信號調制成已知的單頻信號與話音信號一起發送,確保PTT控制信號傳輸的可靠性。當內通設備與電臺直接相連時,接口不兼容。因此需要設計一種電臺接口轉換模塊,能夠將單頻信號與話音信號分離開來,實現電臺與內通設備的通信。

現代的大規模FPGA既能處理過去DSP處理器領域的功能,同時又大大地降低專用集成電路方案的風險和前期成本,因此采用FPGA作為核心芯片和先進的數字信號處理技術來開發將為開發帶來諸多的優勢。

1 設計原理

基于FPGA的電臺接口轉換模塊是基于數字信號處理技術,將設備的話音信號通過模/數轉換器轉化為數字信號傳輸到輸入緩沖區,數字話音信號一方面經過FIR(Finite Impulse Response)帶阻濾波器,濾除某一已知的單頻信號,發送到輸出緩沖區,再通過數模轉換器轉化為話音信號,傳輸給電臺;另一方面,通過時頻變換、閾值檢測以及穩定處理三個步驟,檢測出單頻信號,據此產生PTT(Push-to-Talk)控制信號輸出,其接口轉換模塊功能框圖如圖1所示。

2 FFT處理器設計

在Altera可編程邏輯器件中數字信號處理系統設計需要能夠同時具有高速運算以及硬件語言描述的開發工具。Altera DSP Builder集成了這些工具。Altera公司的DSP Builder大大縮短了DSP開發周期,在友好開發環境里它能幫助使用者生成一個有關DSP設計的高級硬件描述語言。IP中的FFT MegaCore function是一個具有良好性能,高度參數化的快速傅里葉變換的進程。該設計采用DSP Builder模型這個共享開發平臺中的Megacore functions完成FFT處理器和FIR陷波濾波器的設計。

I/O數據流結構的設計如下:

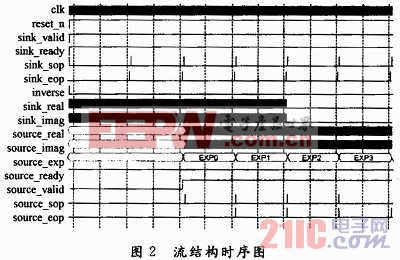

在FFT MegaCore宏功能模塊中主要的參數指標就是數據流相應的時序規則,下面簡要介紹一下流結構的時序原理圖,如圖2所示。

在圖2中,sink_valid是FFT模塊的輸出信號,它表示FFT處理器是否做好接收數據的準備。sink_ready和sink_valid都處于高位時,FFT開始運行,等待sink_sop信號置位開始輸入數據,只要這兩個信號中任一個信號置低位,就表明FFT還未準備好,FFT將處于等待狀態,直到這兩個信號都處于高位才開始運行。sink_sop是一幀信號傳輸的起始信號,sink_eop表示一幀信號傳輸結束信號。

評論