基于FPGA的改進DES算法的實現

此設計方案消除了子密鑰之間的相關性,便于子密鑰在迭代過程中動態分發。同時,簡化了子密鑰的產生,有效地節約了硬件資源。

2.2 單輪迭代運算模塊

DES算法是典型的迭代分組密碼算法,實現過程的核心是16輪次迭代運算。16輪迭代運算過程完全相同,只是輪迭代的輸入參數不同。迭代運算中的輪函數f是非線性的,它是每輪實現擴散和混淆的關鍵。其中,E盒擴展置換和P盒置換都是線性變換,而S盒代換部件是一個十分復雜的非線性函數,正是經過它的非線性變換才使明文實現了較好的混亂,達到加解密的效果,從而具有較強的安全性。因此,S盒設計在整個DES算法中是非常關鍵的。

S盒的功能描述:如果用a1a2a3a4a5a6表示6 bit輸入,那么4 bit的輸出值可以通過查表得到,行的a1a6索引的表示與列的a2a3a4a5索引表示均為二進制數。因此,建立S盒模型時,一般采用case語句來實現。用case多分支選擇語句實現S盒有兩種方法:(1)直接使用輸入為6變量,輸出為4變量的case語句對S盒描述,形成一個4 bit 64個存儲空間的表。此方法可讀性強,但8個S盒需要8×64個存儲空間,占用大量資源,綜合效率低,速度慢,不利于整個系統設計實現; (2)由于S盒是一個4×16的二維數組,使用雙重case語句,外層使用2個變量,對應S盒輸入的第1、6位。內層使用4個變量,對應S盒輸入的第2、3、4、5 位。采用雙重case語句可以直接定位輸出結果。該方案可充分利用FPGA的內部資源,提高綜合效率,加快算法執行速度。經過綜合后,單個S盒的實現僅占用24個邏輯單元,相對于直接使用6個變量的case語句的實現,占用資源約減少50%。

本文對單輪迭代運算進行功能模塊設計,實現過程調用了密鑰生成模塊和S盒模塊。由于該設計的子密鑰是獨立產生的,彼此不相關,因此在一輪運算中,不需把子密鑰輸出作為下輪運算用來產生密鑰的輸入。子密鑰通過控制信號直接控制子密鑰生成模塊產生分發,在一輪運算中只參與與E擴展后的數據進行“異或”運算,既節省了器件的管腳資源,又提高了算法的執行效率。同樣,S盒在具體實例調用時,亦采用了此方法。單輪迭代變換仿真結果如圖4所示。圖中,ki_i為控制子密鑰動態分發的控制信號;L_i和R_i是第i輪非線性變換的輸入;R_i是經過輪函數一系列運算生成的數據與輸入L_i“異或”,產生的結果作為輸出R_o;把R_i直接賦值給輸出L_o。

2.3 頂層模塊的設計與實現

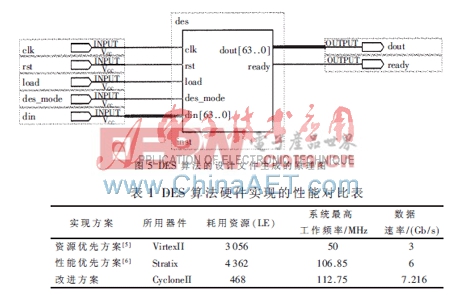

頂層模塊的功能就是調用單輪迭代運算模塊,實現16輪次循環迭代,完成DES算法的總體設計。采用組合邏輯設計實現了數據的初始置換IP、輪函數f、子密鑰的產生以及最后的逆初始置換IP-1。圖5所示為DES算法的最終設計工程文件生成的原理圖。

頂層模塊僅在數據裝載控制信號load為高電平時,接收外部數據din;發送控制信號ready為高電平時,輸出dout為有效數據。由于16輪迭代的每一輪運算都要用到上一輪的最后計算結果,并且每輪迭代都是調用單輪迭代運算模塊。因此,設計了算法執行狀態指示位dt,用來協調控制整個DES算法的各輪迭代運算結果的反饋賦值。采用Altera公司的CycloneII系列的EP2C8Q208C8器件作為平臺,在Quartus II 8.0下對Verilog HDL代碼進行綜合,然后布局布線對其進行時序仿真,仿真結果完全符合時序要求,達到了設計目的。由表1給出的DES算法硬件實現性能對比結果表明,在資源使用和實現速度方面,本文算法實現方案都比較理想。DES系統的實現所占用的邏輯單元數僅為468,小于整個硬件資源的6%,可見設計資源得到了極大的優化利用。

本文的創新點:在傳統硬件實現資源優先方案的基礎上,采取在輪函數內部設置流水線結構來提高系統的整體運行速度,既節省了硬件資源,又提高了系統的性能;簡化了子密鑰與外部密鑰的生成關系,消除了各個子密鑰之間的相關性,保證了在子密鑰和數據異或運算的輪函數實現時,子密鑰的動態分發。

通過對整個DES算法的詳細分析,提出了合理的分模塊設計思想,并采用Verilog硬件描述語言對算法進行了驗證仿真。設計文件最終生成的原理圖可以完成DES算法的功能,對其進行適當改進,可以作為功能模塊嵌入到實際系統中,實現通信數據的實時、可靠傳輸,具有一定的實際應用價值。

參考文獻

[1] 王簡瑜, 張魯國. 基于FPGA實現DES算法的性能分析 [J]. 微計算機信息, 2007, 23(3-2): 217-218.

[2] MCLOONE M, MCCANNY J V. High-performance FPGA implementation of DES using a novel method for implementing the key schedule [J]. IEEE, Circuits Devices System. 2003, 150(5): 373-378.

[3] 鄭東, 李祥學, 黃征. 密碼學—密碼算法與協議[M]. 北京: 電子工業出版社, 2009.

[4] STALLINGS W. Cryptography and network security principles and practices[M]. Prentice Hall,1996.

[5] 姚霽, 劉建華, 范九倫. 一種密鑰可配置的DES加密算法的FPGA實現[J].電子技術應用,2009,35(7):145-148.

[6] 張峰, 鄭春來, 耶曉東. DES加密算法的FPGA實現[J].現代電子技術, 2008, 31(7):80-82.

評論