基于FPGA的幅值可調信號發生器設計

摘要:針對信號發生器時輸出頻率精度高和幅值可調的要求,采用直接數字頻率合成(DDS)技術,提出一種基于FPGA的幅值、頻率均可調的、高分辨率、高穩定度的信號發生器設計方案。采用AT89S52單片機為控制器,控制FPGA產生波形的數字信號,結合雙數模(D/A)轉換器及低通濾波器,最終實現輸出信號幅值0~5 V可調,分辨率為10 bits;頻率范圍1 Hz~10 MHz可調,最小分辨率為1 Hz;頻率穩定度優于10-4。信號參數可通過鍵盤進行設置,并在LCD上輸出。由于FPGA的可編程性,易于對系統進行升級和優化。

關鍵詞:FPGA;信號發生器;DDS;單片機;VHDL

直接數字頻率合成(DDS)技術具有相對頻帶寬、頻率轉換時間短、頻率分辨率高、輸出信號相位連續、能夠實現全數字自動化控制等優點,已經逐步成為高性能信號發生器的核心技術。現場可編程門陣列(FPGA)器件具有工作速度快、集成度高、可靠性好和現場可編程等優點,在現代電子設備中的應用越來越廣。

本文采用DDS技術和FPGA芯片設計了一種頻率可調的信號發生器,可輸出正弦波、方波、三角波和鋸齒波等數字信號,其頻率范圍廣,穩定性好,精度高,系統靈活,易于升級。

1 系統總體設計

系統框圖如圖1所示,它由單片機控制模塊、FPGA波形產生模塊、幅度控制模塊、數模轉換(DAC)模塊、低通濾波模塊、鍵盤輸入和液晶顯示模塊組成。FPGA模塊采用DDS技術,可產生正弦波、方波、三角波或鋸齒波的數字信號,經D/A轉換、低通濾波后輸出。其波形類型及頻率大小通過單片機直接控制,輸出信號幅度的控制由單片機通過幅度控制模塊改變數模轉換模塊的參考電壓來間接實現。

2 功能模塊設計

2.1 FPGA模塊

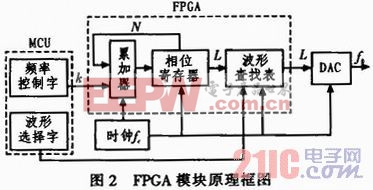

該模塊根據MCU提供的頻率控制字K及波形選擇字,利用DDS技術產生波形數字信號,通過數模轉換器DAC變成階梯波,再經過低通濾波器平滑后就可以得到合成的信號波形。此模塊主要由相位累加器、相位寄存器和波形查找表構成,其原理框圖如圖2所示。其中,fc為輸入基準時鐘頻率,fo為輸出信號頻率,K、N、L分別為頻率控制字、相位累加/寄存器、波形查找表和D/A轉換器的字長。

評論