CPLD與16C554在航空發動機參數采集器中的應用

0 引 言

隨著航空工業和計算機工業的飛速發展,傳統的機械式儀表已經逐漸被數字顯示儀表所替代,嵌入式系統越來越多地應用于航空儀表之中。航空發動機是飛機上最重要的部件之一,需要測量的數據較多,而其各項參數對于駕駛員來說都是非常重要的信息,并且對信號采集的精度和實時性要求非常高。

發動機參數采集顯示系統是航空電子系統的重要組成部分,也是座艙顯示系統的一部分,它在飛行過程中顯示發動機的狀態給飛行員,使飛行員能夠實時了解到發動機的工作情況。發動機參數采集顯示系統由發動機參數采集器和發動機參數顯示器2部分組成。發動機參數采集器的主要功能是對發動機主要傳感器輸出的信號進行調理、采集和處理并輸出給顯示設備進行顯示。隨著航空發動機及其附屬系統越來越復雜,需要測量的參數以及需要進行數據交聯的設備越來越多。這就要求發動機參數采集器具有實時性、可靠性、嵌入性等特點。同時還要考慮到低成本的設計原則和實際工程應用中低功耗的特點。這些條件在系統設計時都需要綜合考慮以達到最優化的性能設計。

隨著集成電路技術的高速發展,可編程專業集成電路的集成度越來越高,功能越來越強大,用可編程邏輯器件進行的集成設計已經逐步取代了基于標準邏輯器件的設計,成為專用集成電路(ASIC)設計的一個重要分支。更重要的是,利用新的Top-Down設計方法,使得系統的設計從一開始就能夠在系統級的行為描述上得到驗證,有效避免了系統設計上的錯誤,減少了設計過程的反復。因此,在嵌入式系統設計中使用可編程邏輯器件,是實現產品小型化、集成化、高可靠性、低成本和低功耗等的有效途徑。

1 航空發動機參數采集器系統概述

航空發動機參數采集器的主要任務是采集發動機以及滑油系統、燃油系統、旋翼和主減速器的各項參數,進行數據處理和數據打包后,通過串行通訊鏈路發送給顯示系統以及其他設備進行顯示或使用;并且當出現告警時,將告警信號發送給告警系統;此外還輸出傳感器激勵電源為傳感器供電。需要采集的參數較多,主要類型有:模擬量、開關量以及頻率量。根據發動機參數采集器系統的信號處理及數據通訊任務的特點,我們采用了美國德州儀器公司(以下簡稱美國TI公司)的TMS320C31浮點型數字信號處理器作為發動機參數采集器的控制核心。TMS320C31是TI公司的浮點型數字信號處理器,它是一種高性能32位微處理器,其內部總線采用了哈佛結構,即程序和數據采用2個獨立的存儲器,每個存儲器獨立編址和取址,故取址和編址能完全重疊運行;并采用流水線作業方式,1個時鐘周期可執行1條指令;片內具有專用硬件乘法器,片上集成有40位浮點運算和其它功能,具有支持邊界掃描測試功能等。TMS320C31處理器的中斷資源包括4種外部中斷:串口發送、接收中斷,2個定時器中斷及DMA中斷,這些均為電平觸發中斷并且都可通過軟件設置來完成。此外,TMS320C311個仿真器接口、2個互鎖信號:XF0、XF1以及其它的保持、復位等信號。TMS320C31上述功能和特點,使得復雜的控制和算法完全可以在規定時間內完成,而且滿足精度要求。

2.1 復雜可編程邏輯器件(CPLD)

可編程邏輯器件通常可分為3大類:通用陣列邏輯(generic array logic)、現場可編程門陣列(fieldprogrammable gate array)和復雜可編程邏輯器件(complex programmable logic device)。CPLD主要是由可編程邏輯宏單元圍繞中心的可編程互連矩陣單元組成。發動機參數采集器系統選用了Xilinx公司的CPLD(XC95144)。按照邏輯關系,編寫出邏輯控制方程,XC95144的程序通過JTAG接口的在線動態可編程專用電纜下載后,即可實現邏輯控制。

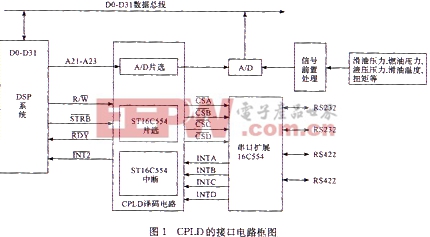

2.2 CPLD的接口電路

利用復雜可編程器件CPLD設計DSP擴展外設電路的譯碼電路,可以使設計者在系統內進行編程,布局、布線都很方便。芯片不必脫離線路板就可以更新設計并下載邏輯電路程序,真正實現了硬件軟件化,從而使開發周期大大縮短,使設計風險大大縮小,CPLD的接口電路框圖如圖1所示。

本文最終實現的發動機參數采集器系統是在原有DSP組成的高速信號處理的基礎上,外加了CPLD芯片構成。接口器件A/D、16C554和DSP的連接完全是通過CPLD實現的。由于使用了CPLD,在PCB設計階段可根據需要調整引腳位置,走線距離縮短,使線路的抗電磁干擾能力增強,有效地減少了PCB設計的工作難度和系統的開發周期。

數據線、地址線等時序信號按照規定的邏輯關系工作。由于CPLD內部采用固定長度的金屬線進行各邏輯塊的互連,所以設計的邏輯電路具有時間的可測性。本文設計所選用的CPLD是Xilinx公司的XC95144芯片,它有144個宏單元,3200個可用邏輯門,100個輸入輸出引腳(81個可用I/O引腳)。這一基于EEPROM的器件能夠提供組合和傳輸延遲在15 ns以內,它的輸入寄存器建立時間非常短,而且能夠提供多個系統時鐘,具有可編程的速度/功率控制。通過對系統所需的邏輯控制信號數目的分析,調試硬件時更改邏輯控制信號。按照邏輯關系,編寫出邏輯控制方程,通過JTAG接口的在線動態可編程用專用電纜下載后,即可實現邏輯控制。

2.3 16C554在串口擴展中的應用

本文所設計的發動機參數采集器系統需要多個串行口與外界進行數據通信,而TI公司的TMS320C31數字信號處理器設計串口的方法一般是利用通用的I/O口線來構成串口,并由軟件來設定波特率。這在DSP使用率較低的情況下比較有用;但是當通信實時性要求較高時,就應該通過擴展異步通信芯片來實現高速串行通信。

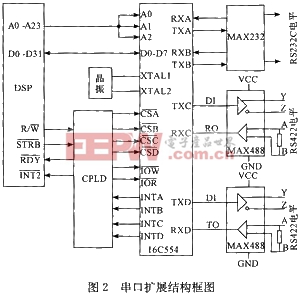

對于并口的設計方法,因為DSP輸入/輸出資源有限,因此,只能利用擴展異步通信芯片或者總線接口來擴展打印口。EXAR公司的異步通信芯片ST16C554正是可以同時實現擴展串行口和并行口通信的理想芯片。該芯片內含4個16C550異步通信單元,每個單元獨立控制發送與接收,且具有16字節FIFO以減少中斷請求次數,波特率發生器可編程。可以利用單一的中斷源來管理多個擴展串口,并保證多個串口中斷的無漏檢測與應答。16C554與DSP的連接如圖2所示。16C554內部共有12個寄存器,可分別用于對通信參數的設置、對線路狀態的訪問、數據的發送和接收以及中斷管理等功能。通過外加電平轉換芯片就可以實現RS232,RS422,RS485通信(本文所設計的發參系統沒有采用RS485通信)。

2.4 串行口中斷處理說明

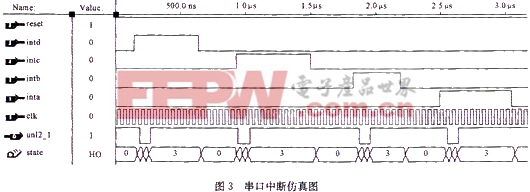

DSP TMS320C31不支持邊沿觸發中斷方式只支持電平觸發中斷方式,而串行口ST16C554為邊沿觸發中斷方式,因此需用CPLD將上邊沿轉化為一個脈寬合適的低電平窄脈沖。由于TMS320C31正H1時鐘的下降沿檢測中斷引腳,因此,低電平窄脈沖的脈寬必須大于一個H1。另一方面,TMS320C31每兩個H1時鐘周期在同一個中斷引腳檢測一次中斷,因此為了使DSP能識別外中斷而且不被重復檢測以免再次進入中斷使系統混亂,必須使低電平窄脈沖的脈寬τ滿足:1T≤τ≤2 T(T為H1/H3的周期)。

因為DSP外部中斷引腳為4個,可用外部中斷只有3個,而4路串口可以產生4個中斷源,因此需通過CPLD處理,最后產生1路中斷送至DSP,處理原理為當4路中任何一路有中斷請求時就產生中斷信號,并將4路中斷的狀態存入寄存器,DSP可利用數據線訪問寄存器以確定具體是哪路產生的中斷。

串行口中斷處理仿真圖如圖3所示,功能是把串行口中斷高電平轉換為2個H3寬度的低脈沖。

3 軟件設計

本文使用的CPLD開發系統是Xilinx公司的ISE 6.x系列,該開發工具功能強大,使用方便。使用美國國防部開發的超高速集成電路硬件描述語言(VHDL)、Verilog公司開發的Verilog HDL和電路圖(schematic)中的任意一種設計方法均可。

3.1 CPLD的邏輯實現

系統通過地址線來對外部接口器件進行尋址,16C554的片選信號是通過CPLD來實現的,下面給出了VerilogHDL描述語言的程序:

3.2 異步串口通信程序的設計

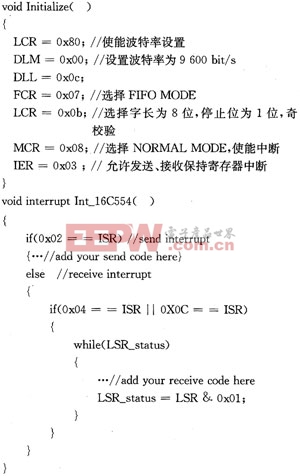

在本系統中,外部晶振頻率為1.843 2MHz,通信格式為8位數據位,1位停止位,奇校驗,工作在中斷方式,16C554四個串口通道各自獨立工作。串口初始化程序以及接收、發送中斷讀取程序如下:

4 結束語

通過16C554擴展串口,其硬件接口電路簡單;復雜可編程器件CPLD的使用,將DSP較強的邏輯控制、數據處理能力以高集成度、高可靠性、高速度有機地結合起來,從而使設計的系統具有較高的性能價格比,設計成本和風險大大降低。

評論