基于SOPC的PCI總線高速數據傳輸系統設計

2.1 系統實現

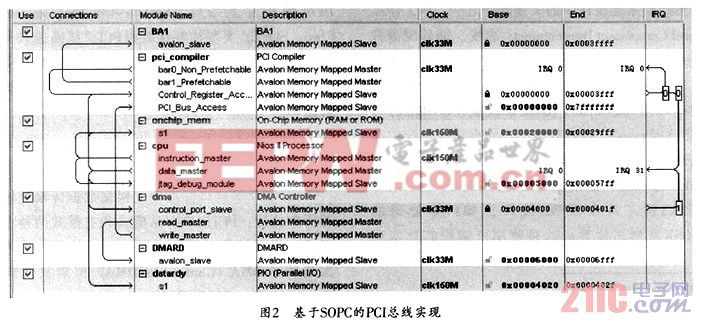

PCI總線接口的SOPC內部結構如圖2所示。實現PCI總線DMA傳輸系統使用到4類功能模塊,分別是實現PCI橋邏輯的pci_comiler組件(pci_c ompiler)、負責數據傳輸的DMA控制器(dma)、控制整個SOPC的NiosII處理器(cpu)及其數據程序存儲器(onchip_mem),以及SOPC和外部用戶邏輯通信的接口模塊(BA1、DMARD和datardy),上述組件通過avalon總線連接在一起組成SOPC。本文引用地址:http://www.j9360.com/article/190791.htm

PCI總線DMA傳輸系統功能模塊之間的交互過程如圖3所示,過程描述如下:

(1)CPU等待PC使能DMA傳輸,PC使能DMA后,執行(2);

(2)PC等待乒乓RAM的數據準備好信號,數據準備好后,執行(3);

(3) CPU將DMA的讀/寫地址和傳輸長度參數寫入DMA控制器中,使能DMA控制器,DMA控制器開始數據傳輸,即讀口通過DMARD接口從RAM中讀數,寫口將數據寫到PCI橋,PCI橋將數據送至PCI總線;

(4)當傳輸結束后,DMA控制器產生一個中斷(IRQ1)送CPU;

(5)CPU判斷傳輸是否完成,傳輸完成則通過PCI橋向PC發送中斷,并執行(1),開始下一次DMA傳輸;

(6)PCI總線發生異常時,PCI橋邏輯中斷CPU,CPU查詢異常狀態,并自動從異常中恢復。

評論