基于FPGA的網絡圖像采集處理系統設計

摘要:介紹一種基于FPGA的網絡圖像采集處理系統設計,該系統采用單片FPGA,實現了圖像的采集、壓縮和網絡傳輸功能,具有體積小,集成度高,算法升級靈活方便的特點。詳述了模塊的圖像采集邏輯、RAM控制邏輯、壓縮算法邏輯和網絡傳輸功能的實現方法。測試結果表明,系統運行穩定,性能滿足要求。

關鍵詞:FPGA;圖像壓縮;網絡傳輸;JPEG

0 引言

隨著網絡技術的發展,網絡化儀器以結構簡單,機動靈活,吞吐率高和成本低等優點而越來越受到重視,并在軍用自動測試裝備中得到廣泛的應用。隨著武器裝備圖像制導技術的廣泛應用,需要對圖像質量等進行評價,因此研制基于網絡的圖像采集處理系統,對提高自動測試裝備的綜合能力具有重要意義。由于FPGA在流水線并行處理數據上具有強大優勢,具有集成度高,體積小,可靈活配置等優點,在圖像處理領域得到廣泛應用。本文介紹一種基于單片FPGA實現圖像采集、處理和網絡傳輸的設計方案。

1 總體設計

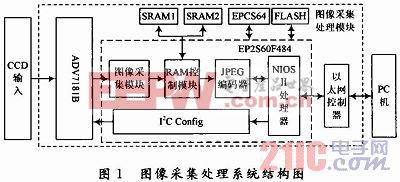

總體框圖如圖1所示,系統采用Altera公司推出的StratixⅡ系列EP2S60F484型號FPGA作為圖像采集處理和網絡傳輸的核心,視頻A/D采用ADV7181B芯片,支持PAL,NTSC和SECAM多種制式視頻輸入。圖像采集處理在FPGA內部實現,主要有3部分,分別為圖像采集模塊、RAM控制模塊和JPEG編碼器。NiosⅡ處理器作為主處理器,主要是通過I2C模塊對ADV7181B進行配置,控制JPEG編碼器和實現圖像的網絡傳輸功能。

2 主要功能模塊設計

2.1 圖像采集模塊

圖像采集模塊主要實現圖像信號檢測和圖像裁剪的功能。

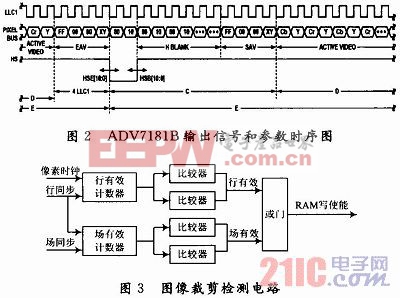

CCD攝像頭輸出的視頻信號經過ADV7181B芯片解碼,輸出符合ITU-R BT.601標準的數據流。圖2所示為ADV7181B輸出的行同步信號參數和YCrCb信號時序圖。當輸出“FF 00 00 XY”時,表示有效圖像數據的開始或者結束。其中XY[4]=0表示圖像數據開始信號(SAV信號);XY[4]=1表示圖像數據結束信號(EAV信號);XY[6]=0表示奇場信號;XY[6]=1表示偶場信號。通過檢測EAV和SAV信號,分奇偶場提取有效的圖像數據。

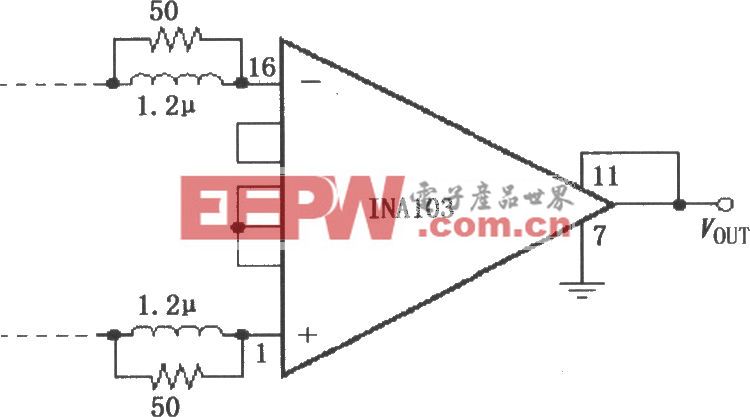

根據輸出圖像大小的不同要求,需要對圖像進行裁剪。構造一個裁剪檢測電路,如圖3所示。利用像素時鐘和水平同步信號、垂直同步信號進行計數,根據圖像輸出大小要求,設定比較器數值,當行列有效計數的數值在比較器設定的范圍之內,檢測電路使RAM處于寫使能狀態,把圖像數據存入RAM。系統默認的圖像輸出大小是720×576像素,如果圖像輸出大小為512×512像素,那么行有效計數中的比較器數值分別為52和308,提取奇場和偶場中的第53行到第308行數據。同理,列有效計數中比較器分別為16和272。

評論