PCI總線從設備接口的CPLD實現

摘要 提出了一種PCI總線從設備的CPLD實現方法。該方法遵從PCI規范2.2版,實現了資源自動配置并且支持數據突發傳輸。試驗證明該方法的有效性,其突發傳輸速率可達20 MB·s-1。

關鍵詞 PCI總線;從設備接口;CPLD

近年來隨著計算機技術的發展,PCI局部總線已逐步取代ISA總線成為家用電腦的標準總線。PCI總線具有總線主控能力,在33 MHz時鐘的工作條件下,突發傳輸速率峰值可達132 MB·s-1;其次它擁有獨立的配置空間,可實現即插即用。這些優點使得PCI總線在數據采集、嵌入式系統和測控等領域得到廣泛應用。

實現PCI總線協議目前主要有專用接口芯片和CPLD實現兩種方式。專用接口芯片使用簡單方便、工作穩定可靠,但往往具體應用中只用到部分功能,并且需要可編程邏輯配合使用,這樣不僅浪費專用芯片的資源,而且也增加了電路板面積。采用Complex Programmable Logic Device(CPLD)實現突出的優點就在于其靈活的可編程性,這使得硬件電路的升級只需改進軟件就可實現,大大提高了硬件平臺的通用性;此外CPLD內部有豐富的邏輯資源,可將用戶控制邏輯和PCI接口邏輯在同一塊芯片中實現,這樣不僅充分利用了邏輯資源,還能使系統設計顯得更加緊湊。

文中主要介紹了采用CPLD實現32 bit 33 MHzPCI從設備接口的設計方法,該從設備接口模塊遵從PCI規范2.2版,實現了資源的自動配置,支持突發傳輸,并為用戶提供了一個簡單的接口。設計完成后配置到一塊PCI開發板上的CPLD中,系統工作穩定、可靠,驗證了該設計方法的工程可行性。

1 PCI總線協議簡介

一個PCI系統中,如果某設備取得了總線控制權,就稱其為主設備;而被主設備選中以進行通信的設備稱為從設備或目標設備。PCI接口信號線共有100根,分為系統信號、仲裁信號、接口控制信號、地址/數據線、錯誤報告信號、中斷信號等類型,其中作為從設備至少需要47條信號線。表1中列出了從設備接口設計必需的接口信號及說明。

一個完整的PCI總線交易過程如下:要發起數據交易的設備先置REQ#,在得到仲裁器的許可(GNT#)后,通過拉低FRAME#啟動一個傳輸交易(TRA NSACTION),并同時在AD[31:0]總線上放置地址,在CBE[3:0]總線上放置命令。PCI總線上所有的設備都對此地址譯碼,被選中的從設備要置DEVSEL#有效以聲明自己被選中,同時對命令譯碼確定訪問類型。在接下來的數據期中,IRDY#和TRDY#分別表示主、從設備準備好。兩者同時有效,則在時鐘上升沿傳輸數據;主從雙方可以分別通過使IRDY#或TRDY#無效,在數據期中插入等待周期。數據傳輸結束前,主設備通過撤銷FRAME#并建立IRDY#標明只剩最后一組數據要傳輸,并在數據傳輸完后放開IRDY#以釋放總線控制權。從設備也可以通過有效STOP#信號來請求終止傳輸,從設備斷開連接有RETRY、DISCONNECT和ABORT3種情況,RETRY是由于數據傳輸的起始字節超過16個PCI時鐘周期引起的;DISCONNECT是由于在數據傳輸的非起始字節,從設備在8個時鐘周期里不能對主設備做出反應引起的;ABORT是由于目標設備發現嚴重錯誤或者不能完成數據請求,而使STOP#和DEVSEL#都無效來終止當前進程。傳輸終止后總線進入空閑狀態,等待下個PCI總線交易開始。

表1中,#表示信號低電平有效,否則為高電平有效。IN表示標準的輸入信號,OUT表示標準的輸出驅動信號,T/S表示雙向的三態輸入/輸出信號,S/T/S表示持續且低電平有效的三態信號,O/D表示漏極開路信號。

2 PCI從設備接口的CPLD實現

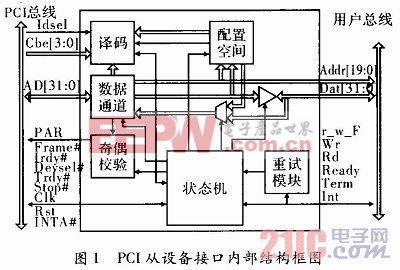

設計的32 bit 33 MHz PCI從設備接口的內部結構框圖如圖1所示,由結構圖可以看出它主要由狀態機、配置空間、譯碼模塊、數據通道、奇偶校驗和重試模塊組成。PCI從設備接口實現的功能是將一個不符合PCI總線協議的設備橋接到PCI總線上,為計算機PCI總線和用戶應用之間傳輸數據提供一個數據通道。該從設備接口為用戶提供了一個簡單的總線接口,特別適合PCI總線與32位SRAM或FIFO等高速存儲設備的橋接。

評論