基于CPLD的RS-232串口通信實現

摘要:為了實現PC機與CPLD的通信,進行了相應的研究。分析了RS-232C通信協議,自定義了數據包傳輸格式。根據UART模塊工作狀態多的特點,應用了有限狀態機理論進行編程實現。為降低誤碼率,應用16倍頻技術,實現了波特率為9 600 bit/s的串口通信。在Quartus II平臺上用VerilogHDL進行編程,并通過了VC編寫程序的數據傳輸的驗證。研究成果為工程上PC機與嵌入式系統數據傳輸的問題提供了一種解決方法。

關鍵詞:RS-232C;UART;CPLD;VerilogHDL;數據包格式;有限狀態機;嵌入式系統

CPLD(Complex Programable Logic Device)是一種復雜的用戶可編程邏輯器件。采用連續連接結構,延時可預測,從而使電路仿真更加準確。CPLD是標準的大規模集成電路產品,可用于各種數字邏輯系統的設計。開發工具Quartus II、ISE等功能強大,編程語言靈活多樣,使設計開發縮短了周期。

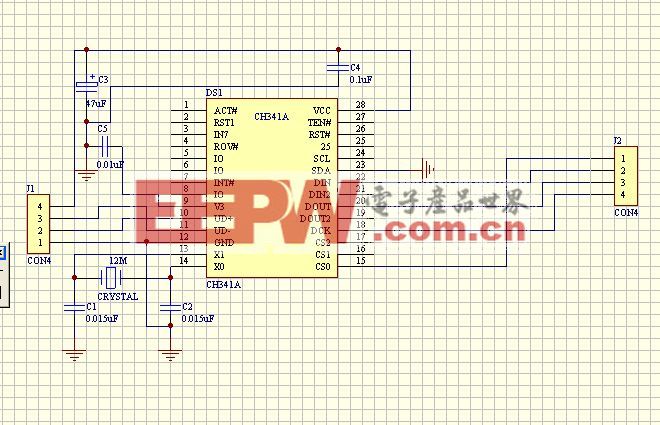

隨著嵌入式的發展,對數據的傳輸和人機交互通信的要求越來越高。而串口通信因其資源消耗少、技術成熟而被廣泛應用。系統中上位機與嵌入式芯片之間的交互通信可以通過專用集成芯片作為外設RS-232異步串行接口,如TI、EXAR、EPIC公司的550、452等系列UAWT集成電路,或在擁有Nios系統的FPGA上可以方便地嵌入UART模塊。但是在設計中用戶會提出自己的要求,如:數據加密或只使用UART部分功能等,即要求更靈活的UART。而且有時CPLD資源剩余,出于成本考慮也會要求設計一種模擬的UART。對于上述的兩種情況,就可以在CPLD其豐富的資源上制作一款UART,實現PC機與嵌入式系統之間的數據交換。

1 串口通信協議

1.1 UART簡介

通用異步收發器(Universal Asynchronous Receiver Transmitter,UART)。異步通信的特點:不要求收發雙方時鐘的嚴格一致,實現容易,設備開銷較小。具有相關工業標準提供的標準的接口電平規范等優點,在工業控制領域被廣泛采用。

異步通信一幀字符信息由4部分組成:起始位、數據位、奇偶校驗位和停止位。

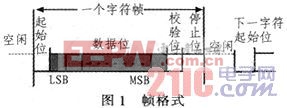

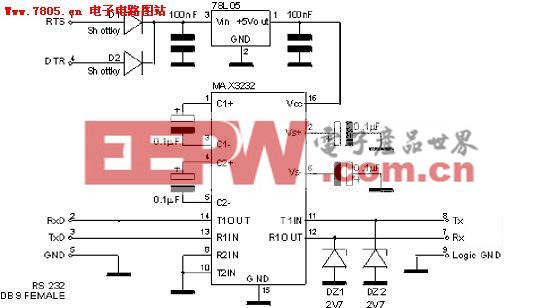

本設計基于RS-232的數據幀結構,設置數據幀結構如圖1所示:1 bit起始位,8 bit數據位,1 bit停止位,無校驗位。每幀實質上傳送1 Byte數據。

1.2 自定義數據包格式

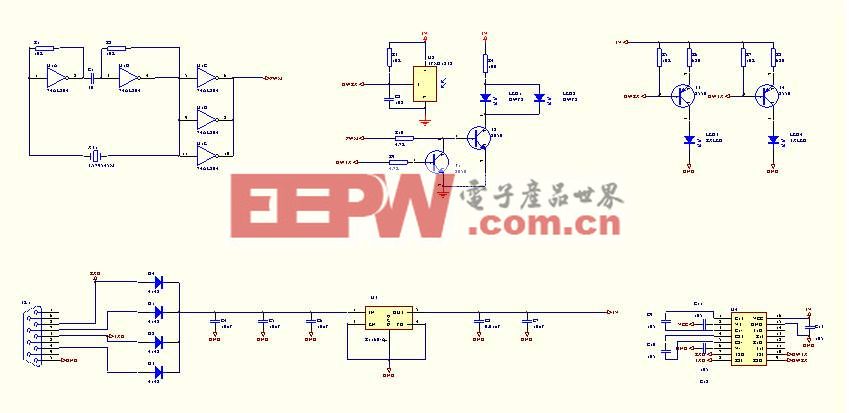

多個上文所描述的幀就可以組成一個數據包。串口通信是在RS-232數據幀結構的基礎上定義的,傳輸以數據包為單位進行。包結構如圖2所示。

本文采用和校驗的結構,一個數據包包含15 Byte。其中第1個字節是數據包頭即握手字符。第2字節為控制字符,EE代表寫命令,DD代表讀命令。第3至第14為可利用數據。第15字節作為校驗字符,理論上應等于這個數據包中數據字符串之和的后8bit。

2 設計方案

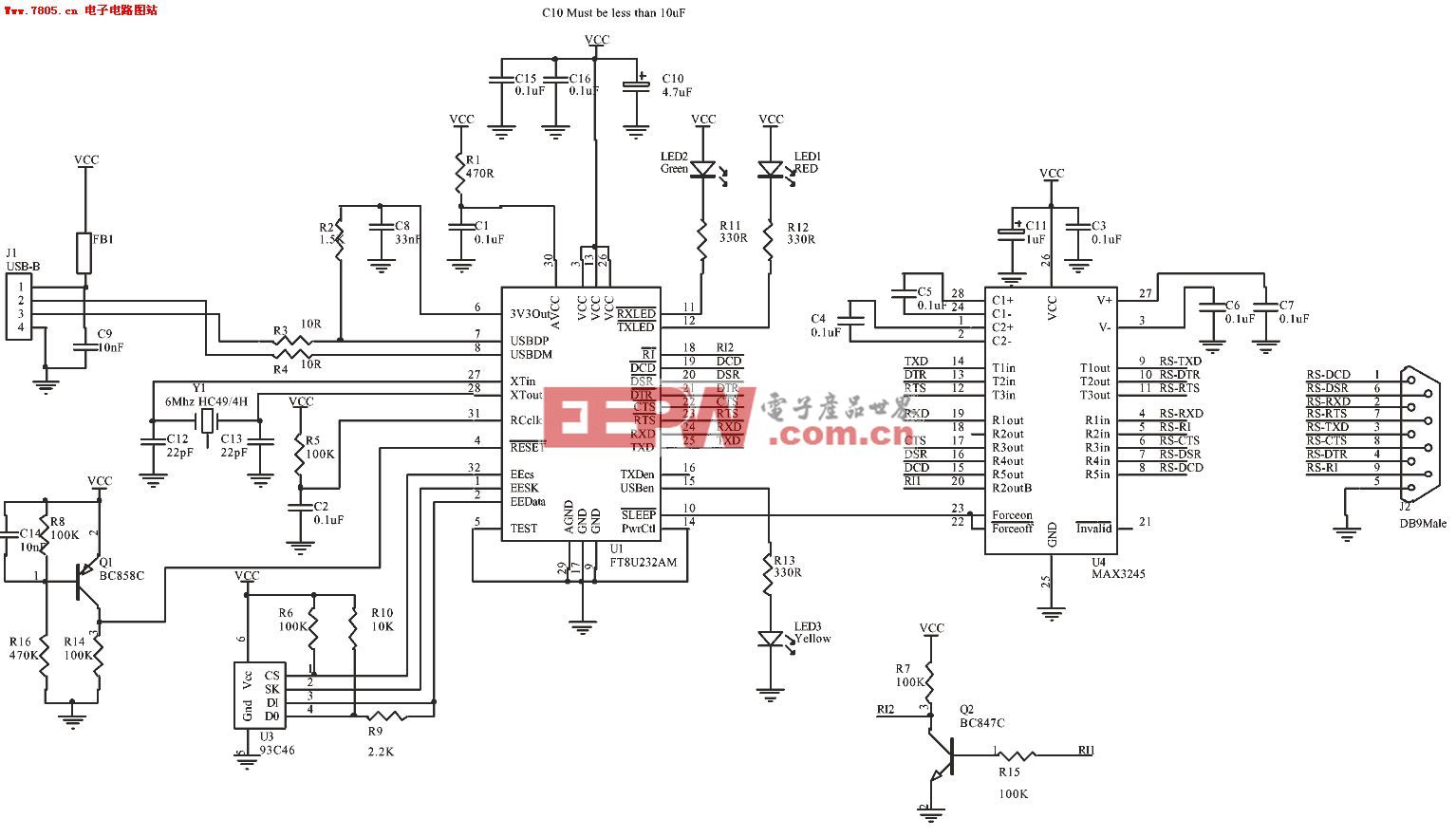

2.1 UART的設計結構

筆者設計采用模塊化設計,方案的UART主要由邏輯控制模塊、波特率發生模塊、發送模塊和接收模塊等組成。波特率發生模塊可以建立精確的時鐘,確保數據采樣準確、工作時序順暢。邏輯控制模塊、波特率發生模塊、發送模塊和接收模塊完成工作有:確定數據起始位、數據收發,串并轉換、建立握手連接、判斷命令、數據校驗等功能。

2.2 狀態圖

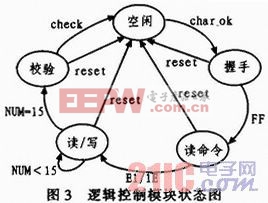

利用串口通信在數據交互過程中涉及到了多種工作狀態,情況比較多樣,而利用程序設計中的有限狀態機(FSM)理論進行編程設計,這個問題可以迎刃而解。

有限狀態機是由寄存器組和組合邏輯構成的硬件時序電路,有限狀態機的狀態(即由寄存器組各位的1和0的組合狀態所構成的有限個狀態)只能在同一時鐘跳變沿的情況下才能從一個狀態轉向另一個狀態。

本設計的有限個狀態編碼使用獨熱碼形式,即寄存器組每一個bit位代表一種狀態(如“0100”,“1000”為四態機中的兩種狀態),這種狀態碼的好處是避免了狀態混亂。狀態機采用Mealy型有限狀態機,這種狀態機的下一個狀態不但取決于各個輸入值,還取決于當前所在狀態,符合UART的工作原理。

邏輯控制模塊、數據接收模塊和發送模塊的設計都使用到了狀態機,其中以邏輯狀態機為主狀態機,其余兩個為從狀態機。確定各種工作狀態和工作流程后便可構建出狀態圖,方便直觀地進行后續設計。

評論